## Dissertation

# Modeling and Simulation of Negative Bias Temperature Instability

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften

eingereicht an der Technischen Universität Wien Fakultät für Elektrotechnik und Informationstechnik von

# Robert Entner

9725877 / E754

Gratweiner Straße 5

8111 Judendorf-Straßengel, Österreich

E-Mail: robert@entner.net

# Abstract

Semiconductor devices and device simulators are well established tools for the reduction of the development time for semiconductor devices. Numerical simulation can help the device engineer to perform dozens of design experiments within the time normally needed to process one single wafer lot. Nowadays simulation efforts go beyond solving the basic semiconductor device equations. Especially the modeling and simulation of aging processes has tremendously gained in importance. This thesis tries to give insight into the topic of semiconductor device simulation and focuses on the modeling of degradation mechanisms.

After a first introduction, giving an overview of the motivation and the structure of this work, the fundamental equations for numerical device simulation, the modeling of generation and recombination mechanisms, as well as the modeling of quantum confinement effects are presented.

The possible defects at the Si/SiO<sub>2</sub> interface are evaluated in the following chapter as this interface is of utmost importance in CMOS technology. An important topic is also the experimental characterization methods of the interface quality.

In the following a thorough investigation on degradation mechanisms affecting the gate dielectric is presented. These are the hot carrier degradation, dielectric wearout and breakdown, and the effect of quantum mechanical tunneling. Here, a new model is proposed for the numerical modeling of trap assisted tunneling currents across several electron traps.

The main part of this work concentrates on negative bias temperature instability (NBTI). NBTI causes degradation of MOS structures at elevated temperatures and negative gate voltages. An elaborate investigation of literature from the first report to the recent understanding of this degradation mechanism is presented. A comprehensive model is derived, combining research results from different groups and the coupling to the basic semiconductor device equations.

The new NBTI model is compared to measurement data and gives excellent results. Furthermore the susceptibility of CMOS circuits as the CMOS inverter, an SRAM cell, and a ring oscillator to NBTI is investigated in mixed mode device and circuit simulations. Stationary and transient simulations show the impact of degradation on real life circuits.

# Kurzfassung

HALBLEITER Prozess- und Bauelementsimulatoren sind etablierte Werkzeuge um die Entwicklungszeiten von Halbleiterprozessen so kurz wie möglich zu halten. Unter Zuhilfenahme numerischer Simulation kann der Bauelementingenieur dutzende Experimente in der Zeit durchführen, in der auf herkömmliche Weise nur die Herstellung eines einzigen Siliziumloses möglich ist. Heutzutage werden nicht mehr nur die grundlegenden Halbleitergleichungen gelöst. Vor allem die Modellierung und Simulation von Alterungsprozessen hat stark an Bedeutung gewonnen. Diese Arbeit gibt Einblick in das Thema Halbleitersimulation, wobei der Schwerpunkt auf der Modellierung dieser Degradationsmechanismen liegt.

Nach einer Einleitung, welche Überblick über Motivation und Struktur dieser Arbeit vermittelt, werden die grundlegenden Gleichungen zur numerischen Bauelementsimulation, die Modellierung von Generations- und Rekombinationsmechanismen sowie der räumlichen Quantisierung präsentiert.

Nachfolgend werden mögliche Defekte an der  $\mathrm{Si/SiO_2}$  Grenzfläche beschrieben, da die Qualität dieses Überganges von höchster Bedeutung für die CMOS Technologie ist. Ebenso wird auf die experimentelle Charakterisierung eingegangen.

Im Weiteren folgt eine genaue Untersuchung von Alterungsprozessen welche das Gate Dielektrikum betreffen. Diese sind Hot Carrier Degradation, Dielectric Wearout und Dielectric Breakdown sowie das quantenmechanische Tunneln. Es wird ein neues Modell vorgeschlagen, welches zur numerischen Betrachtung von störstellenunterstütztem Tunneln über mehrere Elektronenfallen dient.

Der Hauptteil dieser Arbeit konzentriert sich auf den Alterungseffekt der Negative Bias Temperature Instability (NBTI). Er führt zur Degradation von MOS Strukturen bei erhöhten Temperaturen und negativen Gate Spannungen. Es werden wissenschaftliche Arbeiten zum Thema NBTI vom ersten Bericht bis zum heutigen Wissensstand präsentiert. Ein umfassendes Modell wird vorgeschlagen, welches Forschungsergebnisse verschiedener Gruppen zusammenfasst und das Degradationsmodell mit den Halbleitergleichungen kombiniert.

Das neue Modell wird mit Messdaten verglichen und liefert exzellente Übereinstimmung. Weiters wird die Anfälligkeit von CMOS Schaltungen, wie dem CMOS Inverter, einer SRAM Zelle und eines Ringoszillators, in kombinierten Bauelement- und Schaltungssimulationen untersucht. Stationäre sowie transiente Simulationen zeigen den Einfluss von NBTI auf diese Schaltungen.

# Acknowledgment

I WOULD like to express my deep gratitude to a number of people who supported me during my work in technical, financial, and personal form.

First of all I want to thank Prof. Tibor Grasser for giving me the opportunity to work in the Christian Doppler Laboratory for TCAD in Microelectronics at the Institute for Microelectronics. He was the supervisor of this thesis and without his scientific support the high quality of this work would not have been possible. The financial support by the Christian Doppler Gesellschaft allowed me to fully concentrate on the scientific work in combination with an industrial background, thanks to our industry partners Austriamicrosystems and Infineon. A big thank you goes to Prof. Magerl who agreed to take part in the examination committee. I would like to thank Gilbert Declerck, Guido Groeseneken, Robin Degraeve, and Ben Kaczer who gave me the opportunity to work at IMEC research center in Leuven, Belgium, during a two month internship.

I want to thank Prof. Siegfried Selberherr and Prof. Erasmus Langer who are responsible for the excellent working conditions at the Institute for Microelectronics. Both, the technical infrastructure and the amicable climate at the institute assisted me with my task. Also the support of Manfred Katterbauer and Ewald Haslinger in administrative and technical aspects is highly appreciated.

Of highest importance during my time at the Institute for Microelectronics was the endless support of my colleagues and friends. First and foremost I want to name Enzo Ungersböck. We shared our office and had literally uncountable discussions about computer problems, our fatherhood, where to go for lunch, or just daily business. In him I have found a very good friend. The proof-readers of my thesis, Oliver Triebl, Wolfgang Gös, and Philipp Hehenberger with their numerous suggestions greatly improved this work. Furthermore I want to thank Alireza Sheikholeslami, Andreas Gehring, Andreas Hössinger, Christian Hollauer, Gerhard Karlowatz, Gregor Meller, Johann Cervenka, Markus Karner, Martin Vasicek, Martin Wagner, Paul Wagner, Philipp Schwaha, Robert Wittmann, Siddhartha Dhar, Stefan Holzer, Stephan Wagner, Viktor Sverdlov, and Wilfried Wessner, who let me share their knowledge on semiconductors, programming, or operating system related topics.

Above all I want to thank my family. My loving wife Anna supported and encouraged me whenever possible. She brought me through the hard times when work seemed to find no end. My parents, who gave me the opportunity to attend university and who took the financial burden, especially my mother, who raised and guided me. My mother-in-law was supporting my wife and me with our children whenever possible.

And, of course, there are Sarah and Johanna. My daughters are most certainly the best achievement of my life . . .

# Contents

|   | Abs  | tract   |                                           | i   |

|---|------|---------|-------------------------------------------|-----|

|   | Kur  | zfassu  | ng                                        | ii  |

|   | Ack  | nowle   | $\operatorname{dgment}$                   | iii |

|   | Con  | tents   |                                           | iv  |

|   | List | of Ab   | obreviations and Acronyms                 | ix  |

| 1 | Intr | oducti  | ion                                       | 1   |

| 2 | Sim  | ulatio  | n of Semiconductor Devices                | 3   |

|   | 2.1  | Classic | cal Semiconductor Device Equations        | 3   |

|   |      | 2.1.1   | Maxwell's Equations                       | 4   |

|   |      | 2.1.2   | Poisson's Equation                        | 4   |

|   |      | 2.1.3   | Continuity Equations                      | 5   |

|   |      | 2.1.4   | Current Relations                         | 6   |

|   |      |         | 2.1.4.1 Carrier Drift                     | 6   |

|   |      |         | 2.1.4.2 Carrier Diffusion                 | 6   |

|   |      |         | 2.1.4.3 Drift-Diffusion Current Relations | 7   |

|   |      | 2.1.5   | The Semiconductor Equations               | 7   |

|   | 2.2  | Analy   | tic MOSFET Approximations                 | 8   |

|   |      | 2.2.1   | Interface and Oxide Charges               | 8   |

|   |      | 2.2.2   | The Basic Models                          | 8   |

|   |      | 2.2.3   | NBTI Related Models                       | 9   |

|   | 2.3  | Carrie  | er Generation and Recombination           | 10  |

|                                  |     | 2.3.1                   | Photon Transition                               | 0 |

|----------------------------------|-----|-------------------------|-------------------------------------------------|---|

|                                  |     | 2.3.2                   | Phonon Transition                               | 1 |

|                                  |     |                         | 2.3.2.1 Dynamic Case                            | 6 |

|                                  |     |                         | 2.3.2.2 Stationary Case                         | 6 |

|                                  |     |                         | 2.3.2.3 Surface Generation/Recombination        | 7 |

|                                  |     |                         | 2.3.2.4 Distributed Traps                       | 7 |

|                                  |     | 2.3.3                   | Auger Generation/Recombination                  | 8 |

|                                  |     | 2.3.4                   | Impact Ionization                               | 9 |

|                                  | 2.4 | Quant                   | um Mechanical Effects                           | 1 |

|                                  |     | 2.4.1                   | Quantum Confinement                             | 1 |

|                                  |     |                         | 2.4.1.1 Density of States Correction            | 2 |

|                                  |     |                         | 2.4.1.2 Conduction Band Edge Correction         | 3 |

|                                  |     |                         | 2.4.1.3 Evaluation of Quantum Correction Models | 4 |

| 3                                | The | Silico                  | n/Silicon-Dioxide Interface 2                   | 8 |

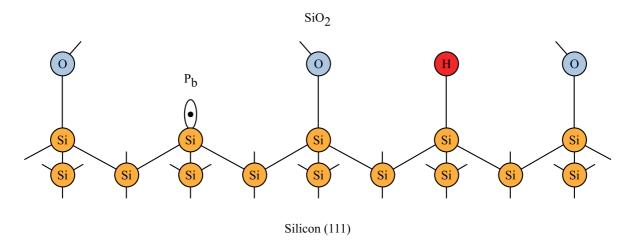

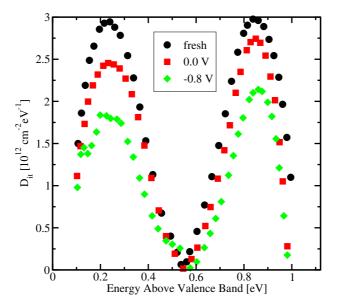

|                                  | 3.1 | Silicon                 | Dangling Bonds                                  | 8 |

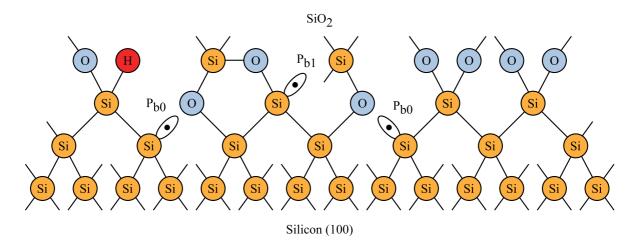

|                                  |     | 3.1.1                   | Amphoteric Nature of Dangling Bonds             | 9 |

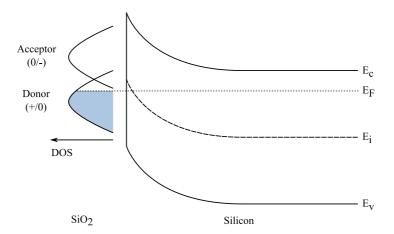

|                                  |     | 3.1.2                   | Characterization of Trap Centers                | 2 |

|                                  |     | 3.1.3                   | Effects of Trap Centers                         | 4 |

|                                  | 3.2 | E' Cei                  | nters                                           | 4 |

| 4 Characterization of Interfaces |     | ization of Interfaces 3 | 6                                               |   |

|                                  |     | e Pumping Method        | 6                                               |   |

|                                  |     | 4.1.1                   | Experimental Setup                              | 6 |

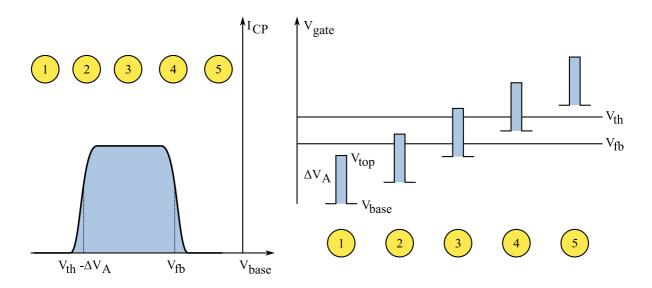

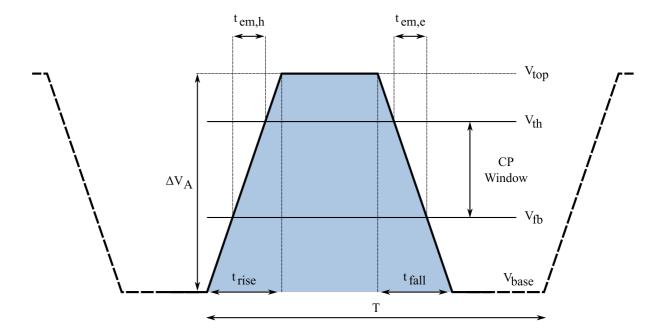

|                                  |     | 4.1.2                   | Charge Pumping Current Model                    | 9 |

|                                  |     | 4.1.3                   | Numerical Simulation                            | 0 |

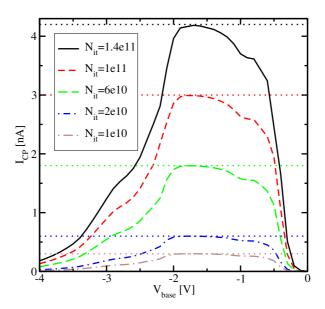

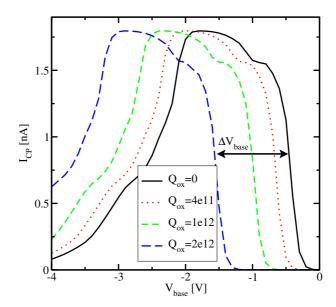

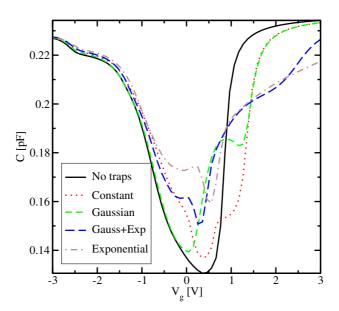

|                                  |     |                         | 4.1.3.1 $D_{\rm it}$ Variation                  | 0 |

|                                  |     |                         | 4.1.3.2 $Q_{\text{ox}}$ Variation               | 2 |

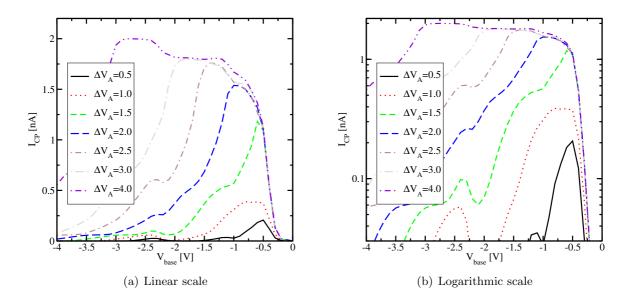

|                                  |     |                         | 4.1.3.3 Pulse Amplitude Variation               | 2 |

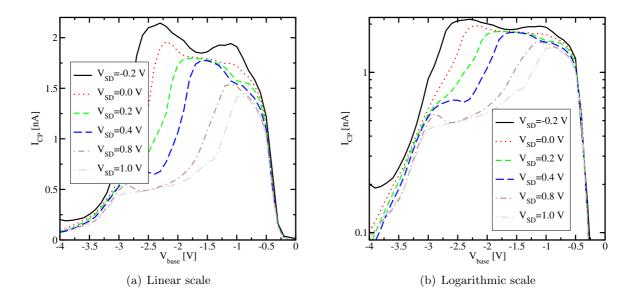

|                                  |     |                         | 4.1.3.4 Reverse Bias                            | 3 |

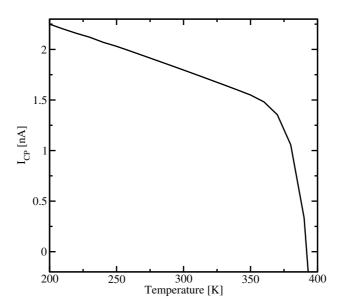

|                                  |     |                         | 4.1.3.5 Temperature Dependence                  | 4 |

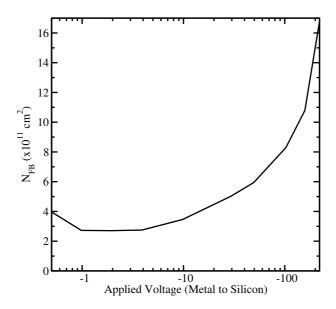

|                                  | 4.2 | DCIV                    | Method                                          | 4 |

|                                  | 4.3 | Capac                   | itance-Voltage Characteristics                  | 6 |

|                                  |     |                         |                                                 |   |

| 5 | Die                               | $\mathbf{lectric}$     | Degradation and Failure Mechanisms            | <b>49</b> |

|---|-----------------------------------|------------------------|-----------------------------------------------|-----------|

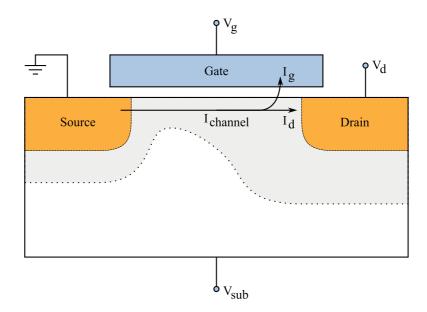

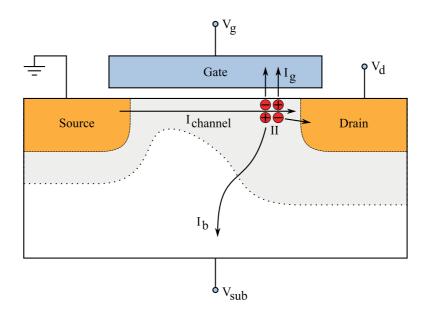

|   | 5.1                               | Hot C                  | Carrier Degradation                           | 49        |

|   |                                   | 5.1.1                  | Channel Hot-Electron Injection                | 50        |

|   |                                   | 5.1.2                  | Drain Avalanche Hot-Carrier Injection         | 50        |

|   |                                   | 5.1.3                  | Secondarily Generated Hot-Electron Injection  | 51        |

|   |                                   | 5.1.4                  | Substrate Hot-Electron/Hole Injection         | 51        |

|   | 5.2                               | Dielec                 | tric Wearout and Breakdown                    | 52        |

|   |                                   | 5.2.1                  | Measurement of Breakdown                      | 52        |

|   |                                   | 5.2.2                  | Models                                        | 52        |

|   |                                   |                        | 5.2.2.1 Anode Hole Injection Model            | 52        |

|   |                                   |                        | 5.2.2.2 Electron Trap Generation Model        | 53        |

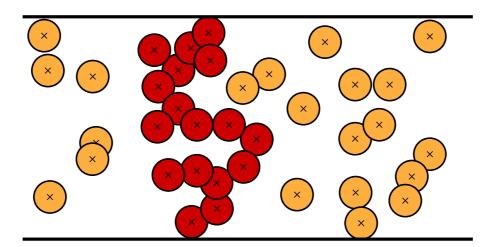

|   |                                   |                        | 5.2.2.3 Percolation Model                     | 53        |

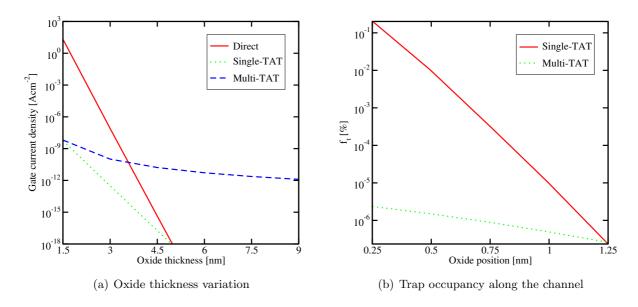

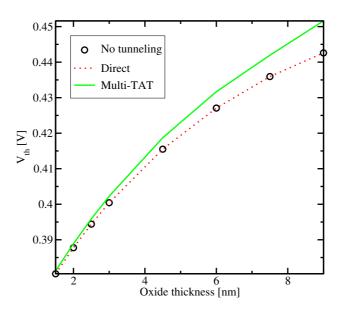

|   | 5.3                               | Quant                  | tum Mechanical Tunneling                      | 54        |

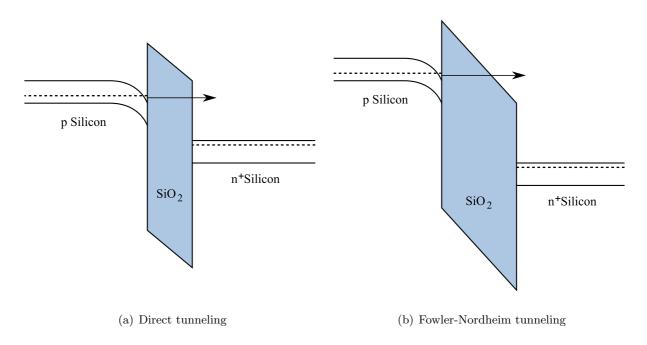

|   |                                   | 5.3.1                  | Direct Tunneling                              | 54        |

|   |                                   |                        | 5.3.1.1 Fowler-Nordheim Tunneling             | 55        |

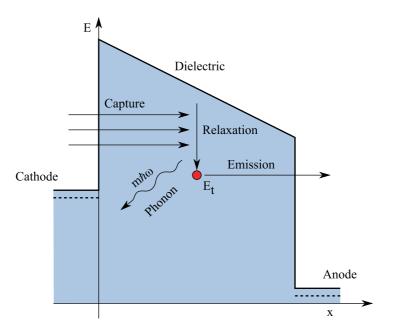

|   |                                   | 5.3.2                  | Trap-Assisted Tunneling                       | 56        |

|   |                                   |                        | 5.3.2.1 Inelastic Phonon-Assisted Tunneling   | 56        |

|   |                                   |                        | 5.3.2.2 Single-Trap Assisted Tunneling        | 57        |

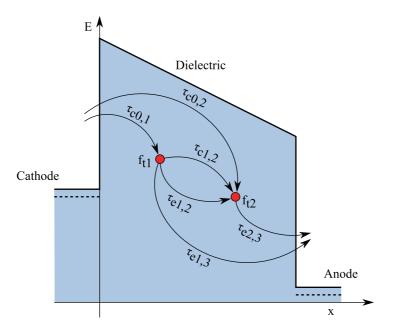

|   |                                   |                        | 5.3.2.3 Multi-Trap Assisted Tunneling         | 58        |

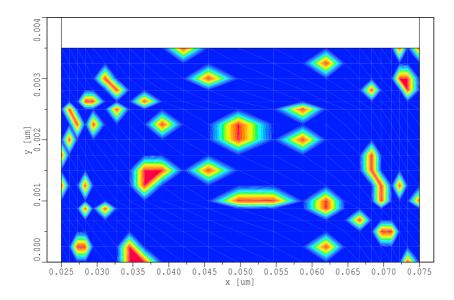

|   |                                   |                        | 5.3.2.4 Influence on the Threshold Voltage    | 60        |

|   | 5.3.3 Evaluation of the New Model |                        | Evaluation of the New Model                   | 61        |

| 6 | Neg                               | gative [               | Bias Temperature Instability                  | 64        |

|   | 6.1                               | First 1                | Report of NBTI                                | 65        |

|   | 6.2                               | The NBTI Time Exponent |                                               | 66        |

|   | 6.3                               | Physic                 | cal Mechanisms of NBTI                        | 66        |

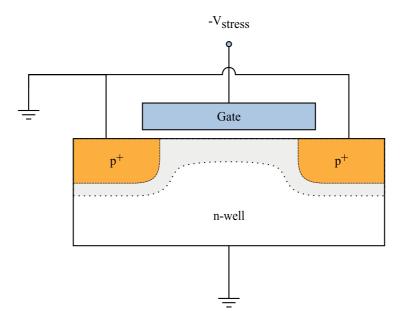

|   |                                   | 6.3.1                  | Basic Experimental Set-Up                     | 67        |

|   |                                   | 6.3.2                  | Faster Determination of the Threshold Voltage | 68        |

|   |                                   | 6.3.3                  | Drain Pulsed Voltage                          | 69        |

|   |                                   | 6.3.4                  | Gate Pulsed Voltage                           | 70        |

|   |                                   | 6.3.5                  | Observation of Terminal Currents              | 71        |

|   |                                   | 6.3.6                  | Importance of Initial Degradation             | 71        |

|   |                                   | 6.3.7                  | pMOSFET vs. nMOSFET                           | 73        |

|   |                      | 6.3.7.1 Charge States                                | 73 |

|---|----------------------|------------------------------------------------------|----|

|   |                      | 6.3.7.2 Availability of Hydrogen                     | 75 |

|   |                      | 6.3.7.3 Work Function Difference                     | 75 |

|   |                      | 6.3.8 Influence of Channel Carrier Transport         | 75 |

|   | 6.4                  | Reaction-Diffusion Model                             | 76 |

|   |                      | 6.4.1 Properties of the R-D Model                    | 77 |

|   |                      | 6.4.2 R-D Model vs. Fast Recovery                    | 79 |

|   |                      | 6.4.3 Dispersive Transport                           | 81 |

|   |                      | 6.4.4 Coupling to the Semiconductor Device Equations | 83 |

|   | 6.5                  | Tsetseris' Model                                     | 83 |

|   | 6.6                  | The New Model for Numerical Simulation of NBTI       | 85 |

|   |                      | 6.6.1 Interface Degradation                          | 86 |

|   |                      | 6.6.2 Drift-Diffusion                                | 87 |

|   |                      | 6.6.3 Trapping                                       | 88 |

| 7 | Cas                  | se Studies                                           | 90 |

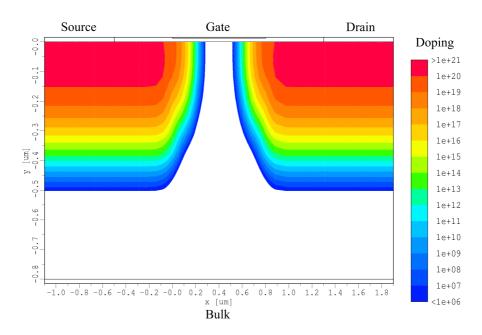

|   | 7.1                  | Power MOS Devices                                    | 90 |

|   |                      | 7.1.1 LDMOSFET                                       | 91 |

|   |                      | 7.1.2 Parameter Extraction                           | 92 |

|   |                      | 7.1.3 Measurements and Simulation Results            | 96 |

|   | 7.2                  | CMOS Inverter                                        | 98 |

|   |                      | 7.2.1 Voltage Transfer Characteristics               | 99 |

|   |                      | 7.2.2 Steady State Degradation                       | 00 |

|   |                      | 7.2.3 Transient Behavior                             | 02 |

|   | 7.3                  | 6T SRAM Cell                                         | 02 |

|   |                      | 7.3.1 Static Noise Margin                            | 05 |

|   |                      | 7.3.2 Steady State Degradation                       | 05 |

|   | 7.4                  | Ring Oscillator                                      | 07 |

|   |                      | 7.4.1 Frequency Degradation                          | 07 |

|   |                      | 7.4.2 Transient Degradation                          | 08 |

| 8 | Sun                  | nmary and Conclusions 1                              | 13 |

|   | $\operatorname{Bib}$ | liography                                            | 14 |

| CONTENTS |

|----------|

|----------|

| Own Publications | 124 |

|------------------|-----|

| Curriculum Vitae | 126 |

# List of Abbreviations and Acronyms

BJT ... Bipolar junction transistor BTI ... Bias temperature instability

CETD ... Critical electron trap density

CHE ... Channel hot electron CMOS ... Complementary MOS

CV ... Capacitance-voltage

DAHC ... Drain avalanche hot carrier

DCIV ... Direct current current voltage

DOS ... Density of states

DRAM ... Dynamic random access memory

DUT ... Device under test

ESD ... Electrostatic discharge

ESR ... Electron spin resonance

GPV ... Gate pulsed voltage

HBM ... Human body model

IV ... Current-voltage

MOS ... Metal-oxide-semiconductor

MOSFET ... MOS field-effect transistor

NBT ... Negative bias temperature

NBTI ... Negative bias temperature instability

nMOSFET ... n-channel MOSFET pMOSFET ... p-channel MOSFET

SDR ... Spin dependent recombination SGHE ... Secondary generated hot electron

SHE ... Substrate hot electron

SILC ... Stress-induced leakage current

SNM ... Static noise margin

SRAM ... Static random access memory

SRH ... Shockley-Read-Hall

TAT ... Trap assisted tunneling

TCAD ... Technology computer-aided design TDDB ... Time dependent dielectric breakdown

VTC ... Voltage transfer characteristic VLSI ... Very large scale integration

# Chapter 1

# Introduction

THE invention of the transistor in 1947 has started the exponential growth of an industry which is now, some decades later, a several hundred billion dollar industry. The first bipolar transistor was announced in December 1947 by William Shockley, John Bardeen, and Walter Brattain at Bell Labs. In 1956 the three researchers were honored with the Nobel Price in physics for their invention. The first metal-oxide-semiconductor (MOS) transistor and the first integrated circuits were demonstrated in the early 1960s. From that time on the development in the field of microelectronics was impressive. The integration density grew exponentially. This exponential growth was already identified in 1965 by Gordon Moore [1] as follows

"The complexity for minimum component costs has increased at a rate of roughly a factor of two per year (...) Certainly over the short term this rate can be expected to continue, if not to increase. Over the longer term, the rate of increase is a bit more uncertain, although there is no reason to believe it will not remain nearly constant for at least 10 years. That means by 1975, the number of components per integrated circuit for minimum cost will be 65,000. I believe that such a large circuit can be built on a single wafer."

Today, in 2007, we have more than 1 billion transistors on one single processor die. This high integration density has to be accompanied by stringent efforts to increase the reliability of each transistor, of the interconnect structure, the packaging, and the whole die to a maximum possible. The failure of a single transistor can lead to complete failure of the whole system.

Not only the integration density has been steadily growing, also the pressure on the industry to deliver short time-to-marked and therefore minimal research and development times for new technology nodes is increasing. This has led to intense efforts in the field of numerical simulation of the semiconductor manufacturing process and the resulting device structure, so called technology computer aided design (TCAD). It can reduce the number of test cycles with real semiconductor devices and drastically increase the possibilities to vary process parameters as doping concentrations, device geometries, materials and their composition to a minimum. Here, TCAD gives the opportunity to analyze the effect of process variation within hours instead of weeks for real processing.

The main target of this thesis is to extend the capabilities of the TCAD framework by a very important degradation mechanism, the negative bias temperature instability (NBTI). This degradation mechanism especially affects p-channel MOS field effect transistors (MOSFETs) which are stressed with negative gate voltages at elevated temperatures. NBTI has gained tremendous scientific and industrial interest as it can lead to severe shifts of important transistor parameters, as the threshold voltage or the drain current, and seems to be accelerated in recent technologies which rely on nitrided oxides, high-k dielectrics, and other novel approaches. The exact physical background is still not completely understood but the general consensus is that the Si/SiO<sub>2</sub> interface is damaged and interface traps and/or interface charges and probably oxide charges cause the degradation.

The structure of this thesis is designed to guide the reader from the fundamental basics of semiconductor device simulation, over the most important degradation mechanisms leading to the thorough elaboration of the effect of NBTI. Presenting the state-of-the-art scientific understanding of this form of device degradation, a comprehensive model is proposed and evaluated by the simulation of a range of case studies.

Chapter 2 presents the fundamental equations for semiconductor device simulation and their derivation from Maxwell's equations and also analytic MOSFET approximations. Next, the most important generation and recombination mechanisms found in semiconductor devices are presented. Here, the main focus is laid upon the phonon transition, or Shockley-Read-Hall, mechanism. It is of special interest for modeling the carrier generation and recombination at silicon/dielectric interface traps which are caused by negative bias temperature instability. The third part of this chapter gives an insight into modeling of quantum confinement at the silicon/dielectric interface.

Chapter 3 focuses on the silicon/silicon-dioxide interface. It is of utmost importance for the proper operation of CMOS technology. NBTI affects exactly this interface and generates defects which are discussed in this chapter. Chapter 4 shows possible means of characterizing the interface using the charge pumping method, the DCIV method, and capacitance-voltage measurements.

Chapter 5 gives an overview of common degradation mechanisms affecting the dielectric layer in CMOS transistors. Sources of degradation outlined here are the damage caused by hot carriers, the dielectric wear-out and breakdown, and quantum mechanical tunneling. The problem of trap-assisted tunneling through highly degraded devices is described in detail. It causes not only additional gate leakage currents but also threshold voltage shifts due to trapped carriers in the oxide, comparable to NBTI.

The main part of this thesis is found in Chapter 6. Here the history of negative bias temperature instability is presented along with the current understanding of the physical mechanisms involved. Methods for measuring the level of degradation are examined and common models trying to reflect the physics of NBTI are presented and discussed. The last part of this chapter presents the new model which was implemented in a numerical device simulator as part of this work. This new model can achieve excellent agreement with measurement data and is especially valuable for the evaluation of pure  $SiO_2$  dielectrics as used in power MOSFETs.

Chapter 7 gives case studies of the presented model which is compared to measurement data and achieves excellent agreement. The impact of NBTI on circuit performance is evaluated in transient and stationary numerical device simulations.

# Chapter 2

# Simulation of Semiconductor Devices

Often based on trial and error steps where different processing parameters such as the exact doping profile, geometries, and temperatures are evaluated. Since the possible combinations are literally unlimited, it is very important to have highly skilled device engineers working on this task. But still, as every new experiment takes up to weeks until the results are obtained and the expenses for fabrication are very high, alternatives or at least assistance in device development is of crucial importance. This is where semiconductor device simulation comes into play. Not only can different geometries and doping profiles be analyzed within hours, simulation also gives detailed insight into the device behavior.

Measurement data mainly concentrate on electrical characterization of the extrinsic data, semi-conductor devices can deliver. These can be the voltage-current relations, the capacitance-voltage curves, or similar. Using simulation tools, also distributed quantities inside the semi-conductor can be explored. This can be for example the carrier concentration, the electrostatic potential, the carrier temperature, or the current density. By using these software tools, the device engineer can gain additional information about how processing changes can alter the intrinsic properties of the semiconductor device.

# 2.1 Classical Semiconductor Device Equations

The semiconductor device equations can be used to describe the whole simulation domain of a semiconductor device. They are applied to the bulk semiconductor, the highly doped regions such as source and drain, and to dielectric regions such as the gate dielectric. In this section the classical semiconductor device equations are presented which are widely used for device simulation and their derivation.

## 2.1.1 Maxwell's Equations

The equations developed by James Clerk Maxwell describe the behavior of electric and magnetic fields and their interaction with matter. They were published by Maxwell in 1864 [2] and in its original form comprised of 20 equations in 20 unknowns. Later they were reformulated in vector notation to the following form

$$\vec{\nabla} \times \vec{E} = -\frac{\partial \vec{B}}{\partial t} \,, \tag{2.1}$$

$$\vec{\nabla} \cdot \vec{B} = 0 \,, \tag{2.2}$$

$$\vec{\nabla} \times \vec{H} = \vec{J} + \frac{\partial \vec{D}}{\partial t} \,, \tag{2.3}$$

$$\vec{\nabla} \cdot \vec{D} = \rho \,. \tag{2.4}$$

Here,  $\vec{E}$  is the electric field,  $\vec{H}$  the magnetic field,  $\vec{D}$  the displacement vector, and  $\vec{B}$  the magnetic flux density vector.  $\vec{J}$  denotes the conduction current density,  $\rho$  is the electric charge density, and  $\partial/\partial t$  is the partial derivative with respect to time.

Equation (2.1) expresses the generation of an electric field due to a changing magnetic field (Faraday's law of induction), (2.2) predicts the absence of magnetic monopoles (magnetic sources or sinks), (2.3) reflects how an electric current and the change in the electric field produce a magnetic field (Ampere-Maxwell law), and finally (2.4) correlates the creation of an electric field due to the presence of electric charges (Gauss' law).

We are using the Maxwell's equations to derive parts of the semiconductor device equations, namely the Poisson equation and the continuity equations.

# 2.1.2 Poisson's Equation

Poisson's equation correlates the electrostatic potential  $\Phi$  to a given charge distribution  $\rho$ . It can be derived from (2.4) using the relation between the electric displacement vector and the electric field vector,

$$\vec{D} = \hat{\varepsilon} \cdot \vec{E} \,, \tag{2.5}$$

where  $\hat{\varepsilon}$  is the permittivity tensor. This relation is valid for materials with time independent permittivity. As materials used in semiconductor devices normally do not show significant anisotropy of the permittivity,  $\hat{\varepsilon}$  can be considered as a scalar quantity  $\varepsilon$  in device simulation. The total permittivity is obtained from the relative  $\varepsilon_r$  and the vacuum permittivity  $\varepsilon_0$  as  $\varepsilon = \varepsilon_r \varepsilon_0$ . Table 2.1 gives an overview of relative permittivity constants for some materials commonly used in semiconductor devices.

As  $\nabla \times \vec{E} = 0$  for the stationary case  $\vec{E}$  can be expressed as a gradient field of a scalar potential field

$$\vec{E} = -\vec{\nabla}\Phi. \tag{2.6}$$

Substituting (2.5) and (2.6) in (2.4) we get

$$\vec{\nabla} \cdot \hat{\varepsilon} \cdot \vec{\nabla} \Phi = -\rho. \tag{2.7}$$

| Material         | Relative Permittivity |

|------------------|-----------------------|

| Si               | 11.7                  |

| GaAs             | 12.5                  |

| Ge               | 16.1                  |

| $\mathrm{SiO}_2$ | 3.9                   |

| $HfO_2$          | $\sim 25$             |

| $HfSiO_4$        | $\sim$ 15–18          |

| $\rm ZrO_2$      | $\sim$ 20–25          |

**Table 2.1:** Relative permittivity constants for materials used in or considered for semiconductor devices.

As we consider the permittivity a scalar, which is constant in homogeneous materials, we obtain Poisson's equation

$$\vec{\nabla} \cdot \vec{\nabla} \Phi = -\frac{\rho}{\varepsilon} \,. \tag{2.8}$$

The space charge density  $\rho$  consists of

$$\rho = q(p - n + C), \qquad (2.9)$$

where q is the elementary charge, p and n the hole and electron concentrations, respectively, and C the concentration of additional, typically fixed, charges. These fixed charges can originate from charged impurities of donor  $(N_{\rm D})$  and acceptor  $(N_{\rm A})$  type and from trapped holes  $(\rho_p)$  and electrons  $(\rho_n)$ ,

$$C = N_{\rm D} - N_{\rm A} + \rho_p - \rho_n$$

(2.10)

The inclusion of trapped carriers is important for the simulation of the impact of degradation on the device performance (Section 2.2, Section 5.3.2, Chapter 6).

Together (2.8) and (2.9) lead to the form of Poisson's equation commonly used for semiconductor device simulation

$$\vec{\nabla} \cdot \vec{\nabla} \Phi = -\frac{\mathbf{q}}{\varepsilon} (p - n + N_{\mathrm{D}} - N_{\mathrm{A}} + \rho_p - \rho_n). \tag{2.11}$$

# 2.1.3 Continuity Equations

The continuity equations can be derived from (2.3) by applying the divergence operator,  $\vec{\nabla}$ , to the equation and considering that the divergence of the curl of any vector field equals zero

$$\vec{\nabla} \cdot \vec{\nabla} \times \vec{H} = \vec{\nabla} \cdot \vec{J} + \vec{\nabla} \cdot \frac{\partial \vec{D}}{\partial t} = 0.$$

(2.12)

Separating the total current density  $\vec{J}$  into hole and electron current densities,  $\vec{J} = \vec{J}_p + \vec{J}_n$ , and using (2.4) and (2.9) gives

$$\vec{\nabla} \cdot \vec{J_n} + \vec{\nabla} \cdot \vec{J_p} + q \left( \frac{\partial p}{\partial t} - \frac{\partial n}{\partial t} + \frac{\partial N_D}{\partial t} - \frac{\partial N_A}{\partial t} + \frac{\partial \rho_p}{\partial t} - \frac{\partial \rho_n}{\partial t} \right) = 0.$$

(2.13)

When we consider the charged impurities as time invariant and introduce a quantity R to split up (2.13) into separate equations for electrons and holes, we get

$$\vec{\nabla} \cdot \vec{J_n} - q \frac{\partial n}{\partial t} - q \frac{\partial \rho_n}{\partial t} = qR, \qquad (2.14)$$

$$\vec{\nabla} \cdot \vec{J_p} + q \frac{\partial p}{\partial t} + q \frac{\partial \rho_p}{\partial t} = -qR. \qquad (2.15)$$

The quantity R gives the net recombination rate for electrons and holes. A positive value means recombination, a negative value means generation of carriers. Models for R are presented in Section 2.3.

#### 2.1.4 **Current Relations**

There are two major effects which lead to current flow in silicon. First, the drift of charged carriers due to the influence of an electric field, and second, the diffusion current due to a concentration gradient of the carriers.

#### 2.1.4.1 Carrier Drift

Charged carriers in a semiconductor subjected to an electric field are accelerated and acquire a certain drift velocity. The orientation depends on the charge state, holes are accelerated in direction of the electric field and electrons in opposite direction. The magnitude of the drift velocity depends on the statistical probability of scattering events. At low impurity concentration, the carriers mainly collide with the crystal lattice. Is the impurity concentration higher the collision probability with the charged dopants through Coulomb interaction becomes more and more likely, thus reducing the drift velocity with increasing doping concentration.

For low electric fields, the drift component of the electric current can be expressed in terms of Ohm's law as

$$\vec{J}_n^{\text{drift}} = \sigma_n \vec{E} \,, \tag{2.16}$$

$$\vec{J}_n^{\text{drift}} = \sigma_n \vec{E},$$

(2.16)

$\vec{J}_p^{\text{drift}} = \sigma_p \vec{E}.$  (2.17)

Here,  $\sigma$  denotes the conductivity and can be expressed in terms of carrier mobilities for electrons and holes,  $\mu_n$  and  $\mu_p$ , as

$$\sigma_n = q n \mu_n \,, \tag{2.18}$$

$$\sigma_p = qp\mu_p. (2.19)$$

The mobility for electrons is, due to their lower effective mass, about three times higher than for holes.

#### 2.1.4.2 Carrier Diffusion

A concentration gradient of carriers leads to carrier diffusion. This is because of their random thermal motion which is more probable in the direction of the lower concentration. The current contribution due to the concentration gradient is written as

$$\vec{J}_n^{\text{diff}} = q D_n \vec{\nabla} n \,, \tag{2.20}$$

$$\vec{J}_p^{\text{diff}} = -q D_p \vec{\nabla} p. \tag{2.21}$$

Here,  $D_n$  and  $D_p$  are the diffusion coefficients for electrons and holes, which can, in thermal equilibrium for non-degenerate semiconductors, be expressed in terms of the mobility using the Einstein relation

$$D_n = \frac{\mathbf{k_B}T}{\mathbf{q}}\mu_n\,, (2.22)$$

$$D_p = \frac{\mathbf{k_B}T}{\mathbf{q}}\mu_p. \tag{2.23}$$

### 2.1.4.3 Drift-Diffusion Current Relations

Combining the current contributions of the drift and the diffusion effect we get

$$\vec{J_n} = qn\mu_n \vec{E} + qD_n \vec{\nabla} n, \qquad (2.24)$$

$$\vec{J}_p = qp\mu_p \vec{E} - qD_p \vec{\nabla} p. \tag{2.25}$$

# 2.1.5 The Semiconductor Equations

With the Poisson equation (2.11), the continuity equations for electrons and holes (2.14) (2.15), and the drift-diffusion current relations for electron- and hole-current (2.24) (2.25) we now have a complete set of equations which can be seen as fundamental for the simulation of semiconductor devices:

$$\vec{\nabla} \cdot \vec{\nabla} \Phi = -\frac{\mathbf{q}}{\varepsilon} (p - n + C) , \qquad (2.26)$$

$$\vec{\nabla} \cdot \vec{J_n} - q \frac{\partial n}{\partial t} - q \frac{\partial \rho_n}{\partial t} = qR, \qquad (2.27)$$

$$\vec{\nabla} \cdot \vec{J_p} + q \frac{\partial p}{\partial t} + q \frac{\partial \rho_p}{\partial t} = -qR, \qquad (2.28)$$

$$\vec{J}_n = qn\mu_n \vec{E} + qD_n \vec{\nabla} n , \qquad (2.29)$$

$$\vec{J_p} = qp\mu_p \vec{E} - qD_p \vec{\nabla} p. \tag{2.30}$$

These equations, not including the charge contribution of trapped carriers, have first been published by VanRoosbroeck in 1950 [3].

This set of equations is widely used in numerical device simulators and provides only the basics for device simulation. In modern simulators they are accompanied by higher order current relation equations like the hydrodynamic, six-, or eight-moments models. There are models for the carrier mobility, the carrier generation and recombination (Section 2.3), for quantum effects like quantum mechanical tunneling (Section 5.3) or quantum confinement (Section 2.4.1) and of course for modeling of device degradation, as negative bias temperature instability (Chapter 6).

# 2.2 Analytic MOSFET Approximations

For the simulation of electronic circuits it is often of interest to have compact models for the involved devices. In comparison to solving the semiconductor device equations using compact models reduces the simulation time drastically. Compact models can also be a good guide on what effects the change of physical quantities has on the device characteristics.

The disadvantage is that for each device the right model has to be chosen and the according model parameters have to be extracted. Furthermore, it is not possible to investigate novel device geometries or new materials without processing the device and obtaining an adequate model first.

# 2.2.1 Interface and Oxide Charges

A change in the interface and oxide charges ( $\Delta Q_{\rm it}$  and  $\Delta Q_{\rm ox}$ ) contributes to a threshold voltage shift  $\Delta V_{\rm th}$  as

$$\Delta V_{\rm th} = \frac{\Delta Q_{\rm it} + \Delta Q_{\rm ox}}{C'}, \qquad (2.31)$$

where C' is the capacitance per unit area of the oxide.

In the context of NBTI interface charges are usually the result of charged interface defects  $D_{\rm it}$ . The interface charge depends on the Fermi-level  $E_{\rm F}$  and the trap occupancy f and can be calculated as [4]

$$Q_{\rm it} = q_0 \int D_{\rm it}(E) f(E_{\rm F}, E) dE. \qquad (2.32)$$

Charged oxide traps  $D_{\text{ox}}$  contribute to the threshold voltage shift depending on their position in the dielectric. The resulting, effective,  $Q_{\text{ox}}$  can be evaluated as [5]

$$Q_{\text{ox}} = q_0 \int \int D_{\text{ox}}(x, E) f(x, E) (1 - x/t_{\text{ox}}) dx dE.$$

(2.33)

Here,  $t_{ox}$  is the oxide thickness.

### 2.2.2 The Basic Models

A very common compact model for the MOSFET is the Level 1 model implemented in the circuit simulator SPICE. There the threshold voltage is obtained as

$$V_{\rm th} = V_{\rm T0} + \gamma \left( \sqrt{2\phi_p - V_{\rm bs}} - \sqrt{2\phi_p} \right) + \frac{Q_{\rm it} + Q_{\rm ox}}{C'},$$

(2.34)

where  $V_{\rm T0}$  is the threshold voltage for  $V_{\rm bs}=0\,{\rm V}$  and  $\gamma$  the body-effect parameter, defined as

$$\gamma = \frac{\sqrt{2\varepsilon_{\rm S}q_0N_{\rm A}}}{C'} \,. \tag{2.35}$$

Here,  $\varepsilon_{\rm S}$  is the permittivity of the silicon substrate and  $N_{\rm A}$  the acceptor doping concentration. The potential in the neutral p-type region  $\phi_p$  is evaluated as

$$\phi_p = \frac{\mathbf{k_B}T}{\mathbf{q_0}} \ln \frac{N_{\mathbf{A}}}{n_{\mathbf{i}}} \,. \tag{2.36}$$

During NBTI stress this threshold voltage is shifted due to trapped charges by  $\Delta V_{\rm th}$  obtained from (2.31).

In the linear regime, where

$$V_{\rm gs} > V_{\rm th}$$

and  $V_{\rm ds} < V_{\rm gs} - V_{\rm th}$  (2.37)

the drain current is obtained as

$$I_{\rm ds} = \mu C' \frac{W}{L_{\rm eff}} \left( V_{\rm gs} - V_{\rm th} - \frac{V_{\rm ds}}{2} \right) V_{\rm ds} (1 + \lambda V_{\rm ds}).$$

(2.38)

Here,  $\mu$  is the effective carrier mobility, W the device width,  $L_{\rm eff}$  the effective gate length, and  $\lambda$  is an empirical parameter reflecting the channel length modulation.

In the saturation regime, where

$$V_{\rm gs} > V_{\rm th}$$

and  $V_{\rm ds} > V_{\rm gs} - V_{\rm th}$  (2.39)

the drain current is modeled as

$$I_{\rm ds} = \frac{\mu C'}{2} \frac{W}{L_{\rm eff}} (V_{\rm gs} - V_{\rm th})^2 (1 + \lambda V_{\rm ds}). \tag{2.40}$$

# 2.2.3 NBTI Related Models

In NBTI investigations the degradation of the transconductance  $g_{\rm m}$  is an important figure of merit. The transconductance is defined as the change of drain current as a result of a change in the gate voltage

$$g_{\rm m} = \frac{\Delta I_{\rm d}}{\Delta V_{\rm g}} \,. \tag{2.41}$$

Devine et al. proposed a transconductance shift versus interface trap  $(N_{it})$ , relation as [6]

$$\Delta g_{\rm m} = g_{\rm m0} \frac{\alpha N_{\rm it}}{1 + \alpha N_{\rm it}} \,, \tag{2.42}$$

where  $\alpha$  is a processing related parameter. As mobility model Devine proposed

$$\mu = \frac{\mu_0}{1 + \alpha N_{\rm it}} \,. \tag{2.43}$$

With respect to modeling of NBTI these equations show very well how, for example, a reduction of the carrier mobility reduces the drain current, as does an increase of the threshold voltage.

## 2.3 Carrier Generation and Recombination

Carrier generation is a process where electron-hole pairs are created by exciting an electron from the valence band of the semiconductor to the conduction band, thereby creating a hole in the valence band. Recombination is the reverse process where electrons and holes from the conduction respectively valence band recombine and are annihilated. In semiconductors several different processes exist which lead to generation or recombination, the most important ones are:

- photon transition or optical generation/recombination,

- phonon transition or Shockley-Read-Hall generation/recombination,

- Auger generation/recombination or three particle transitions, and

- impact ionization.

In thermal equilibrium the generation and recombination processes are in dynamic equilibrium. When the system is supplied with additional energy, for example through the absorption of photons or the influence of temperature, additional carriers are generated. The most important generation/recombination processes for the simulation of semiconductor devices are summarized in the following.

## 2.3.1 Photon Transition

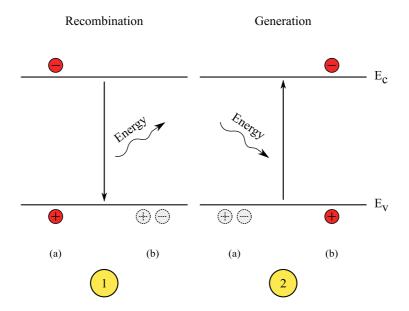

The photon transition is a direct, band-to-band, generation/recombination process. An electron from the conduction band falls back to the valence-band and releases its energy in the form of a photon (light). The reverse process, the generation of an electron-hole pair, is triggered by a sufficiently energetic photon which transfers its energy to a valence band electron which is excited to the conduction band leaving a hole behind. The photon energy for this process has to be at least of the magnitude of the band-gap energy  $E_{\rm g}$ . Figure 2.1 gives an overview of this process. The initial electron/hole constellation is found in (a) while the constellation after the generation/recombination process is found in (b).

For these state changes in the semiconductor the energy and the momentum have to be conserved. The energy is emitted or absorbed via a photon with the energy

$$E = h\nu, (2.44)$$

where h is Planck's constant and  $\nu$  is the frequency of the emitted or absorbed photon. However, as the momentum of a photon is very small no momentum transfer is possible in the transition process. Therefore, only direct band-to-band transitions are possible, where no change in momentum is necessary. As silicon and germanium are indirect semiconductors and have their valence band maximum and their conduction band minimum on different positions in momentum space, direct transitions are very unlikely to occur and can in most cases be neglected for those materials. In direct semiconductors like GaAs, this effect is very important.

Figure 2.1: Direct generation/recombination process. During photon assisted recombination an electron from the conduction band re-combines with a hole in the valence band. The excess energy is transferred to a photon. The reverse process obtains its energy from radiation and generates an electron hole pair.

The process of carrier recombination is directly proportional to the amount of available electrons and holes. By assuming the capture and emission rates  $C_{\rm c}^{\rm OPT}$  and  $C_{\rm e}^{\rm OPT}$  the recombination and generation (G = -R) rates can be written as

$$R_{np}^{\text{OPT}} = C_c^{\text{OPT}} np, \qquad (2.45)$$

$$R_{np}^{\text{OPT}} = C_{\text{c}}^{\text{OPT}} np, \qquad (2.45)$$

$$G_{np}^{\text{OPT}} = C_{\text{e}}^{\text{OPT}}. \qquad (2.46)$$

As the recombination and generation are balanced in thermal equilibrium, where  $np = n_i^2$

$$R_{nn}^{\text{OPT}} = G_{nn}^{\text{OPT}}, \qquad (2.47)$$

$$R_{np}^{\text{OPT}} = G_{np}^{\text{OPT}},$$

(2.47)

$C_{\text{c}}^{\text{OPT}} n_{\text{i}}^2 = C_{\text{e}}^{\text{OPT}},$  (2.48)

the total band-to-band recombination is calculated as the deviation from the thermal equilibrium

$$R^{\text{OPT}} = C_{c}^{\text{OPT}}(np - n_{i}^{2}).$$

(2.49)

This process always strives for thermal equilibrium. For an excess concentration of carriers  $np-n_{\rm i}^2>0$  and carrier recombination dominates, while for low carrier densities  $np-n_{\rm i}^2<0$ and carrier generation prevails.

#### 2.3.2 **Phonon Transition**

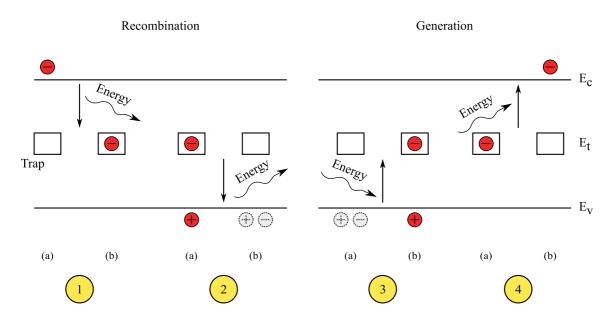

Another process is the generation/recombination by phonon emission. This process is trapassisted utilizing a lattice defect at the energy level  $E_{\rm t}$  within the semiconductor band-gap. The

**Figure 2.2:** Four sub-processes in the Shockley-Read-Hall generation/recombination process.

1. electron capture, 2. hole capture, 3. hole emission, and 4. electron emission.

excess energy during recombination and the necessary energy for generation is transferred to and from the crystal lattice (phonon). A theory describing this effect has been established by Shockley, Read, and Hall [7,8]. Therefore, the effect is throughout the literature referenced as Shockley-Read-Hall (SRH) generation/recombination. Four sub-processes are possible:

- 1. Electron capture. An electron from the conduction band is captured by an empty trap in the band-gap of the semiconductor. The excess energy of  $E_c E_t$  is transferred to the crystal lattice (phonon emission).

- 2. Hole capture. The trapped electron moves to the valence band and neutralizes a hole (the hole is captured by the occupied trap). A phonon with the energy  $E_{\rm t} E_{\rm v}$  is generated.

- 3. Hole emission. An electron from the valence band is trapped leaving a hole in the valence band (the hole is emitted from the empty trap to the valence band). The energy necessary for this process is  $E_{\rm t}-E_{\rm v}$ .

- 4. Electron emission. A trapped electron moves from the trap energy level to the conduction band. For this process additional energy of the magnitude  $E_{\rm c}-E_{\rm t}$  has to be supplied.

These sub-processes are illustrated in Figure 2.2. (a) gives the initial electron/hole constellation, the arrows schematically depict the transition, and (b) gives the constellation after the sub-process.

Both, the recombination and the generation processes are two-step processes. The sequential occurrence of sub-processes 1 and 2 leads to recombination of an electron-hole pair. The excess energy of approximately the band-gap energy is transferred to the crystal lattice via lattice

vibrations, phonons. For the SRH generation of an electron-hole pair sub-processes 3 and 4 are responsible. Here external energy has to be supplied from the lattice.

To derive an expression for the total recombination rate  $R^{\rm SRH}$ , rates for every sub-process are introduced. Here, acceptor like traps are assumed, which are neutral when empty and negatively charged when occupied by an electron. The derivation for donor traps, which are neutral when occupied by an electron and positively charged when empty, is similar and delivers the same result.

The electron capture rate  $v_{\rm ec}$  is proportional to the electron concentration in the conduction band n, the concentration of empty traps  $N_{\rm t}^0$ , and a proportionality constant  $k_{\rm ec}$ . As the available electrons are spread in energy in the conduction band, we must consider the electron capture rate for different energies E. With the energy dependent distribution function for electrons  $f_{\rm e}(E)$  and the density-of-states  $g_{\rm e}(E)$  we get

$$dv_{\rm ec} = k_{\rm ec}(E) N_{\rm t}^0 f_{\rm e}(E) g_{\rm e}(E) dE. \qquad (2.50)$$

This is the differential electron capture rate at energy E. The total amount of conduction band electrons is

$$n = \int_{E_c}^{\infty} f_{\rm e}(E) g_{\rm e}(E) dE.$$

(2.51)

The hole capture rate  $v_{hc}$  is proportional to the hole concentration in the valence band p, the concentration of filled traps  $N_t^-$ , and a proportionality constant  $k_{hc}$ . Again, we consider the spread of the holes in energy,

$$dv_{hc} = k_{hc}(E) N_t^- f_h(E) g_h(E) dE.$$

(2.52)

Here,  $f_h(E)$  is the distribution function for holes and  $g_h(E)$  the density-of-states. The total amount of holes in the valence band is

$$p = \int_{E_{rr}}^{\infty} f_{h}(E) g_{h}(E) dE.$$

(2.53)

The hole emission rate  $v_{\text{he}}$  is proportional to the concentration of empty traps, the proportionality constant  $k_{\text{he}}$ ,

$$dv_{he} = k_{he}(E) N_t^0 (1 - f_h(E)) g_h(E) dE.$$

(2.54)

And finally the electron emission rate  $v_{ee}$  is proportional to the concentration of filled traps and the proportionality constant  $k_{ee}$

$$dv_{ee} = k_{ee}(E) N_t^- (1 - f_e(E)) g_e(E) dE.$$

(2.55)

The total trap concentration  $N_{\rm t}$  is

$$N_{\rm t} = N_{\rm t}^0 + N_{\rm t}^- \,, \tag{2.56}$$

and the fraction of occupied traps  $f_{\rm t}$  is given by

$$f_{\rm t} = \frac{N_{\rm t}^{-}}{N_{\rm t}}, \quad 1 - f_{\rm t} = \frac{N_{\rm t}^{0}}{N_{\rm t}}.$$

(2.57)

With these definitions the net recombination rate for electrons becomes

$$dR_{e}^{SRH} = dv_{ec} - dv_{ee} = \left[k_{ec}(E) N_{t}^{0} f_{e}(E) - k_{ee}(E) N_{t}^{-} (1 - f_{e}(E))\right] g_{e}(E) dE.$$

(2.58)

In thermal equilibrium  $(np = n_0p_0 = n_1^2)$  the net generation equals zero, which means that the respective capture and emission rates for electrons and holes must be equal

$$v_{\rm ec} = v_{\rm ee} \,, \quad v_{\rm hc} = v_{\rm he} \,.$$

(2.59)

From (2.58) we obtain using (2.59)

$$\frac{k_{\rm ee}(E)}{k_{\rm ec}(E)} = \frac{1 - f_{\rm t}}{f_{\rm t}} \frac{f_{\rm e}(E)}{1 - f_{\rm e}(E)}.$$

(2.60)

In thermal equilibrium  $f_t$  is given by Fermi-Dirac statistics

$$f(E) = \frac{1}{1 + \exp\left(\frac{E - E_{\rm F}}{k_{\rm B}T_{\rm L}}\right)},\tag{2.61}$$

with the property

$$\frac{f}{1-f} = \exp\left(-\frac{E - E_{\rm F}}{k_{\rm B}T_{\rm L}}\right). \tag{2.62}$$

The ratio (2.60) then calculates as

$$\frac{k_{\rm ee}(E)}{k_{\rm ec}(E)} = \exp\left(\frac{E_{\rm t} - E_{\rm F}}{k_{\rm B}T_{\rm L}}\right) \exp\left(-\frac{E - E_{\rm F}}{k_{\rm B}T_{\rm L}}\right) = \exp\left(\frac{E_{\rm t} - E}{k_{\rm B}T_{\rm L}}\right). \tag{2.63}$$

Using (2.63) we can further develop (2.58)

$$dR_{e}^{SRH} = \left[ N_{t}^{0} f_{e}(E) - \frac{k_{ee}(E)}{k_{ec}(E)} N_{t}^{-} (1 - f_{e}(E)) \right] k_{ec}(E) g_{e}(E) dE$$

(2.64)

$$= \left[ (1 - f_{\rm t}) f_{\rm e}(E) - \frac{k_{\rm ee}(E)}{k_{\rm ec}(E)} f_{\rm t} (1 - f_{\rm e}(E)) \right] N_{\rm t} k_{\rm ec}(E) g_{\rm e}(E) dE$$

(2.65)

$$= \left[ 1 - \frac{k_{\text{ee}}(E)}{k_{\text{ec}}(E)} \frac{f_{\text{t}}}{1 - f_{\text{t}}} \frac{1 - f_{\text{e}}(E)}{f_{\text{e}}(E)} \right] (1 - f_{\text{t}}) f_{\text{e}}(E) k_{\text{ec}}(E) g_{\text{e}}(E) N_{\text{t}} dE$$

(2.66)

$$= \left[1 - \exp\left(\frac{E_{t} - E}{k_{B}T_{L}}\right) \exp\left(-\frac{E_{t} - E_{Ft}}{k_{B}T_{L}}\right) \exp\left(\frac{E - E_{F}}{k_{B}T_{L}}\right)\right]$$

(2.67)

$$(1 - f_t)f_e(E)k_{ec}(E)g_e(E)N_t dE$$

(2.68)

$$= \left[1 - \exp\left(\frac{E_{\rm Ft} - E_{\rm F}}{k_{\rm B}T_{\rm L}}\right)\right] (1 - f_{\rm t}) f_{\rm e}(E) k_{\rm ec}(E) g_{\rm e}(E) N_{\rm t} dE, \qquad (2.69)$$

with the trap's quasi Fermi energy  $E_{\rm Ft}$ .

Integrating over all possible electron energies gives the total electron recombination rate

$$R_{\rm e}^{\rm SRH} = \left[1 - \exp\left(\frac{E_{\rm Ft} - E_{\rm F}}{k_{\rm B}T_{\rm L}}\right)\right] (1 - f_{\rm t}) N_{\rm t} \int_{E_{\rm c}}^{\infty} f_{\rm e}(E) k_{\rm ec}(E) g_{\rm e}(E) dE. \qquad (2.70)$$

Typically a capture cross section  $\sigma_{\rm e}(E)$  is introduced to rewrite  $k_{\rm ec}$  as

$$k_{\rm ec}(E) = \sigma_{\rm e}(E) v_{\rm th}^{\rm e}, \qquad (2.71)$$

with the thermal velocity for electrons

$$v_{\rm th}^{\rm e} = \sqrt{\frac{3k_{\rm B}T_{\rm L}}{m}},\qquad(2.72)$$

resulting in

$$R_{\rm e}^{\rm SRH} = \left[1 - \exp\left(\frac{E_{\rm Ft} - E_{\rm F}}{k_{\rm B}T_{\rm L}}\right)\right] (1 - f_{\rm t})N_{\rm t}v_{\rm th}^{\rm e} \int_{E_{\rm c}}^{\infty} f_{\rm e}(E)\sigma_{\rm e}(E)g_{\rm e}(E)dE. \qquad (2.73)$$

For non-degenerate semiconductors near equilibrium a Maxwell-Boltzmann distribution can be assumed

$$f(E) = \exp\left(-\frac{E - E_{\rm F}}{k_{\rm B}T_{\rm L}}\right), \qquad (2.74)$$

and one obtains for the integral in (2.73)

$$n\langle\!\langle \sigma_{\rm e} \rangle\!\rangle = \int_{E_{\rm e}}^{\infty} \exp\left(-\frac{E - E_{\rm F}}{k_{\rm B}T_{\rm L}}\right) \sigma_{\rm e}(E) g_{\rm e}(E) dE,$$

(2.75)

with the properties

$$n = N_{\rm c} \exp\left(-\frac{E_{\rm c} - E_{\rm F}}{k_{\rm B}T_{\rm L}}\right)$$

and  $K_{\rm ec} = N_{\rm t} \langle\langle k_{\rm ec} \rangle\rangle = N_{\rm t} v_{\rm th}^{\rm e} \langle\langle \sigma_{\rm e} \rangle\rangle$ , (2.76)

where  $N_{\rm c}$  is the effective density-of-states for electrons we have

$$R_{\rm e}^{\rm SRH} = \left[ n - N_{\rm c} \exp\left(-\frac{E_{\rm c} - E_{\rm F}}{k_{\rm B}T_{\rm L}}\right) \exp\left(\frac{E_{\rm Ft} - E_{\rm F}}{k_{\rm B}T_{\rm L}}\right) \right] (1 - f_{\rm t}) K_{\rm ec}, \qquad (2.77)$$

and

$$R_{\rm e}^{\rm SRH} = \left[ n(1 - f_{\rm t}) - N_{\rm c} \exp\left(-\frac{E_{\rm c} - E_{\rm t}}{k_{\rm B}T_{\rm L}}\right) f_{\rm t} \right] K_{\rm ec}. \tag{2.78}$$

Introducing the auxiliary quantity

$$n_1 = N_{\rm c} \exp\left(-\frac{E_{\rm c} - E_{\rm t}}{k_{\rm B}T_{\rm L}}\right), \qquad (2.79)$$

we finally get for the electron recombination rate

$$R_{\rm e}^{\rm SRH} = (n(1 - f_{\rm t}) - n_1 f_{\rm t}) K_{\rm ec}.$$

(2.80)

Analogously the hole recombination rate can be obtained as

$$R_{\rm h}^{\rm SRH} = (pf_{\rm t} - p_1(1 - f_{\rm t})) K_{\rm hc},$$

(2.81)

by introducing

$$p_1 = N_{\rm v} \exp\left(\frac{E_{\rm v} - E_{\rm t}}{k_{\rm B}T_{\rm L}}\right). \tag{2.82}$$

### Dynamic Case 2.3.2.1

In transient simulations the capture and emission rates are not equal. Therefore, no further simplifications are possible and an additional equation has to be solved for each trap

$$\frac{\mathrm{d}n_{\mathrm{t}}}{\mathrm{d}t} = R_{\mathrm{e}}^{\mathrm{SRH}} - R_{\mathrm{h}}^{\mathrm{SRH}}.$$

(2.83)

This increases the computational effort significantly but is necessary for example to simulate the charge pumping effect (Section 4.1).

#### 2.3.2.2**Stationary Case**

In the stationary case electrons and holes always act in pairs thus the recombination rates for electrons and holes are equal,

$$R_n^{\text{SRH}} = R_p^{\text{SRH}} = R^{\text{SRH}} \,. \tag{2.84}$$

Therefore, we can calculate  $f_t$  from (2.80) and (2.81) as

$$f_{\rm t} = \frac{k_{\rm ec}n + k_{\rm hc}p_1}{k_{\rm ec}(n+n_1) + k_{\rm hc}(p+p_1)}.$$

(2.85)

Using this expression for the total recombination rate we get

$$R^{\text{SRH}} = R_n^{\text{SRH}} = k_{\text{ec}} N_{\text{t}} \left( n(1 - f_{\text{t}}) - n_1 f_{\text{t}} \right)$$

(2.86)

$$= k_{\rm ec} N_{\rm t} \left( n \left( 1 - \frac{k_{\rm ec} n + k_{\rm hc} p_1}{k_{\rm ec} (n+n_1) + k_{\rm hc} (p+p_1)} \right) - n_1 \frac{k_{\rm ec} n + k_{\rm hc} p_1}{k_{\rm ec} (n+n_1) + k_{\rm hc} (p+p_1)} \right)$$

$$= k_{\rm ec} k_{\rm hc} N_{\rm t} \frac{np - n_1 p_1}{k_{\rm ec} (n+n_1) + k_{\rm hc} (p+p_1)} .$$

$$(2.87)$$

$$= k_{\rm ec} k_{\rm hc} N_{\rm t} \frac{np - n_1 p_1}{k_{\rm ec} (n + n_1) + k_{\rm hc} (p + p_1)}.$$

(2.88)

It is very common to introduce carrier lifetimes for electrons and holes  $\tau_n$  and  $\tau_p$

$$\tau_n = \frac{1}{k_{\text{pc}} N_{\text{t}}}, \quad \tau_p = \frac{1}{k_{\text{bc}} N_{\text{t}}}.$$

(2.89)

By using the capture cross sections for electrons and holes,  $\sigma_e$  and  $\sigma_h$ , and the thermal velocities  $v_{\rm th}^e$  and  $v_{\rm th}^h$

$$\tau_n = \frac{1}{\sigma_e v_{th}^e N_t}, \quad \tau_p = \frac{1}{\sigma_h v_{th}^h N_t},$$

(2.90)

we come to the final formulation of the Shockley-Read-Hall model for carrier generation/recombination

$$R^{\text{SRH}} = \frac{np - n_{\text{i}}^2}{\tau_p(n+n_1) + \tau_n(p+p_1)}.$$

(2.91)

Regarding the efficiency of trap centers it can be seen that the energy transfer necessary for generation/recombination is always approximately the band-gap energy, no matter where the trap energy level is. The reason is that carriers are transferred from one energy band-edge to the trap level and further to the other band-edge, giving in total the band-gap energy. But when the two sub processes capture and emission are considered, it can be seen that the further the trap energy is away from the mid-gap energy, the higher is the necessary energy for either capture or emission and the lower for the respective other process. The highest energy in this two-step process is always limiting the total generation/recombination. When the trap is located in the middle of the band-gap, the resulting energy barrier height is half the band-gap energy. As the trap is moved away from the mid-gap energy, the limiting energy barrier is increased and the probability of generation/recombination is reduced.

Impurities used for doping semiconductors are usually energetically situated very close to either the valence or the conduction band in order to be effective doping centers. They are therefore not very effective for carrier generation/recombination and are called "shallow" traps. "Deep" traps on the other hand are located close to the mid-gap which can be used to artificially increase the carrier generation or recombination.

## 2.3.2.3 Surface Generation/Recombination

For the investigation of NBTI the generation and recombination mechanisms at the silicon/dielectric interface are of major importance (Chapter 3). The Shockley-Read-Hall generation/recombination mechanism can also be applied to traps at the interface, which is for example obligatory for the simulation of the charge pumping effect (Section 4.1).

The derivation for recombination at surface traps is similar to the derivation for bulk traps. The major difference is the different unit for interface traps  $[N_{\rm it}] = 1/{\rm cm}^2$  and the resulting unit for the surface recombination velocity  $[R_{\rm it}^{\rm SRH}] = 1/{\rm cm}^2$ s.

### 2.3.2.4 Distributed Traps

As described in detail in Section 3.1.1, interface traps are not located on discrete energy levels but distributed in the band-gap instead. When accounting for the trap density-of-states  $D_{it}(E)$ ,

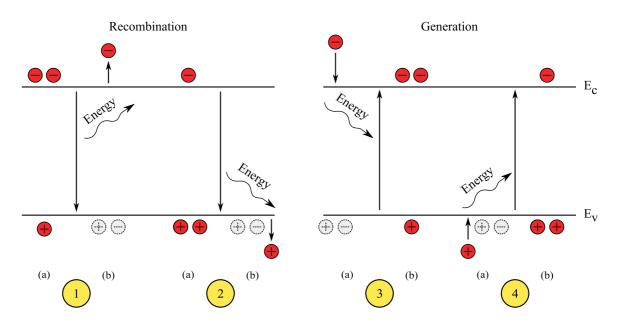

**Figure 2.3:** Four sub-processes in the Auger generation/recombination mechanism. 1. electron capture, 2. hole capture, 3. electron emission, and 4. hole emission.

we get for the interface trap concentration

$$N_{\rm it} = \int_{E_{\rm v}}^{E_{\rm i}} D_{\rm it}(E) dE = \int_{E_{\rm i}}^{E_{\rm c}} D_{\rm it}(E) dE.$$

(2.92)

The interface trap recombination rate is then obtained as

$$R_{\text{it}}^{\text{SRH}} = \int_{E}^{E_c} \frac{np - n_i^2}{\tau_p(n+n_1) + \tau_n(p+p_1)} D_{\text{it}}(E) dE.$$

(2.93)

# 2.3.3 Auger Generation/Recombination

In the direct band-to-band Auger mechanism three particles are involved. During generation an electron hole pair is generated consuming the energy of a highly energetic particle. In the opposite process, when an electron hole pair recombines, the excess energy is transferred to a third particle. In detail the four possible processes are as follows:

- 1. Electron capture. An electron from the conduction band moves to the valence band neutralizing a hole in the valence band. The excess energy is transferred to an electron in the conduction band.

- 2. Hole capture. Again, an electron from the conduction band moves to the valence band and recombines with a valence hole. The excess energy is, in contrast to Process 1, transferred to another *hole* in the valence band.

- 3. Electron emission. A highly energetic electron from the conduction band transfers its energy to an electron in the valence band. The valence electron moves to the conduction band generating an electron hole pair.

- 4. Hole emission. A highly energetic hole from the valence band transfers its energy to an electron in the valence band which is then excited to the conduction band generating an electron hole pair.

These sub-processes are illustrated in Figure 2.3. (a) gives the initial electron/hole constellation, the arrows schematically depict the transition, and (b) gives the constellation after the sub-process.

As for the Shockley-Read-Hall effect a model can be derived by setting up rates for the four processes. For electron capture two electrons in the conduction band and one hole in the valence band are necessary. Using  $k_{\rm ec}$  as the rate constant, the electron capture rate  $v_{\rm ec}$  becomes

$$v_{\rm ec} = k_{\rm ec} n^2 p$$

. (2.94)

Analogical for hole capture where two holes and one electron are involved  $v_{\rm hc}$  evaluates as

$$v_{\rm hc} = k_{\rm hc} n p^2$$

. (2.95)

For electron and hole emission only one respective carrier is necessary

$$v_{\rm ee} = k_{\rm ee} n \,, \tag{2.96}$$

$$v_{\rm he} = k_{\rm he} p. \tag{2.97}$$

In thermal equilibrium the respective capture and emission rates are in equilibrium, and therefore

$$v_{\text{ec},0} = v_{\text{ee},0}, \quad k_{\text{ec}} n_{\text{i}}^2 = k_{\text{ee}},$$

(2.98)

$$v_{\rm hc,0} = v_{\rm he,0} \,, \quad k_{\rm hc} n_{\rm i}^2 = k_{\rm he} \,.$$

(2.99)

This leads us to the final model for the Auger recombination rate  $R^{AUG}$

$$R^{\text{AUG}} = v_{\text{ec}} + v_{\text{hc}} - v_{\text{ee}} - v_{\text{he}} = (k_{\text{ec}}n + k_{\text{hc}}p)(np - n_{\text{i}}^2). \tag{2.100}$$

Although the Auger mechanism is microscopically exactly the same as the mechanism during impact ionization described in the next section, the energy source is completely different. Whereas impact ionization relies on high current density, only a very large carrier density is of importance for Auger generation/recombination, as can be seen in the final formulation of (2.100).

## 2.3.4 Impact Ionization

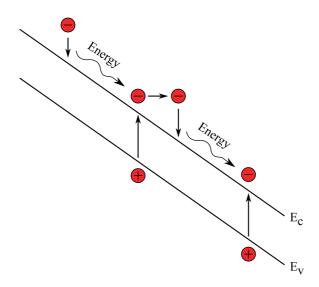

Impact ionization is a pure generation process. Microscopically it is exactly the same mechanism as the generation part of the Auger process: a highly energetic carrier moves to the conduction or valence band, depending on the carrier type, and the excess energy is used to excite an electron

Figure 2.4: Impact ionization and avalanche multiplication. An energetic electron donates its energy to the generation of an electron hole pair. The newly generated electron can, due to the high electric field, obtain high energy and generate further carriers, leading to avalanche multiplication.

from the valence band to the conduction band generating another electron hole pair. The major difference is the cause of the effect. While it is purely the carrier concentration in the Auger mechanism, for impact ionization it is the current density.

Two partial processes can be distinguished:

- 1. Electron emission. A highly energetic electron from the conduction band transfers its energy to an electron in the valence band. The valence electron moves to the conduction band generating an electron hole pair.

- 2. Hole emission. A highly energetic hole from the valence band transfers its energy to an electron in the valence band which is then excited to the conduction band generating an electron hole pair.

Figure 2.4 depicts the effect of impact ionization and avalanche multiplication. The leftmost, highly energetic, electron excites a new electron/hole pair which gains energy and generates further carriers. The result is an avalanche multiplication of carrier generation.

As already mentioned, the generation rates are modeled proportional to the current densities  $\vec{J_n}$  and  $\vec{J_p}$  and can be written as:

$$v_{\rm e} = \alpha_{\rm e} \frac{|\vec{J}_n|}{q}, \qquad (2.101)$$

$$v_{\rm h} = \alpha_{\rm h} \frac{|\vec{J}_p|}{q}, \qquad (2.102)$$

$$v_{\rm h} = \alpha_{\rm h} \frac{|\vec{J_p}|}{q} \,, \tag{2.102}$$

with the ionization rates for electrons and holes,  $\alpha_{\rm e}$  and  $\alpha_{\rm h}$ . These rates are typically described with an exponential dependence upon the electric field component in the direction of the current flow E. With the critical electric fields for electrons and holes,  $E_{\rm e}^{\rm crit}$  and  $E_{\rm h}^{\rm crit}$ , and the ionization rates at infinite field,  $\alpha_{\rm e}^{\infty}$  and  $\alpha_{\rm h}^{\infty}$ , the ionization rates evaluate as

$$\alpha_{\rm e} = \alpha_{\rm e}^{\infty} \exp\left(-\left(\frac{E_{\rm e}^{\rm crit}}{E}\right)^{\beta_{\rm e}}\right),$$

(2.103)

$$\alpha_{\rm h} = \alpha_{\rm h}^{\infty} \exp\left(-\left(\frac{E_{\rm h}^{\rm crit}}{E}\right)^{\beta_{\rm h}}\right).$$

(2.104)

Here,  $\beta_e$  and  $\beta_h$  are additional model parameters, which are in the range of 1–2. The total impact ionization rate is now found as

$$R^{\rm II} = -v_{\rm e} - v_{\rm h} = -\alpha_{\rm e} \frac{|\vec{J}_n|}{q} - \alpha_{\rm h} \frac{|\vec{J}_p|}{q}$$

(2.105)

The impact ionization rate does not actually depend on the local electric field but on the carrier temperature and, thus, on the high-energy tail of the distribution function. Therefore, the model is not very accurate, especially in small devices. Carriers need to travel a certain distance in the high electric field in order to gain energy. For the exact modeling semiconductor device equations of higher order are necessary.

# 2.4 Quantum Mechanical Effects

The classical semiconductor device equations from Section 2.1 imply that the mobile carriers, electrons and holes, behave like classical particles in the semiconductor. For large device dimensions this assumption gives very good results, but for small device geometries quantum mechanical effects like the quantum mechanical tunneling, described in Section 5.3, and the quantum mechanical confinement gain importance. The latter effect leads to a reduction of allowed states for electrons and holes near a Si/SiO<sub>2</sub> interface. In classical device simulations using the drift-diffusion approximation the peak of the electron concentration in the channel of a turned on n-channel MOSFET is calculated to be directly at the Si/SiO<sub>2</sub> interface. This is not correct as the number of allowed states is drastically reduced close to the interface and therefore the peak of the carrier concentration lies several angstroms away from the interface [9].

## 2.4.1 Quantum Confinement

For the modeling of NBTI the carrier concentration close to the Si/SiO<sub>2</sub> interface plays an important role (Section 6.4.4). The use of quantum confinement models reduces this carrier concentration and might have significant influence on the NBTI model used.

In classical device simulators quantum confinement is often accounted for by using additional quantum correction models. These models locally change the carrier density-of-states [10, 11] or they modify the conduction band edge close to the interface [12].

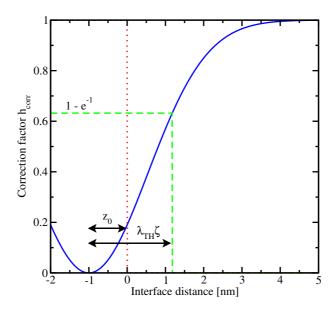

Figure 2.5: Plot of the DOS correction factor  $h_{\text{corr}}$  for  $z_0 = 1 \text{ nm}$  and  $\zeta = 1 \text{ at } T = 300 \text{ K}$ .

## 2.4.1.1 Density of States Correction

In classical device simulation the density-of-states (DOS) in homogeneous materials is modeled as a constant value throughout the device. In order to describe the quantum mechanical confinement a distance-dependent reduction of the DOS at the  $\rm Si/SiO_2$  interface has been proposed in [10,11]

$$h_{\text{corr}} = 1 - \exp\left(-\frac{(z+z_0)^2}{\zeta^2 \lambda_{\text{TH}}^2}\right) ,$$

(2.106)

where z is the distance to the Si/SiO<sub>2</sub> interface and  $z_0$  shifts the whole function relative to the interface.  $\zeta$  is a newly introduced parameter which enables the variation of  $\lambda_{\rm TH}$  for calibration purposes. The symbol  $\lambda_{\rm TH}$  denotes the thermal wavelength which is given by

$$\lambda_{\rm TH} = \frac{\hbar}{\sqrt{2m^* k_{\rm B} T}}, \qquad (2.107)$$

where  $\hbar$  is the reduced Planck constant,  $m^*$  is the effective carrier mass,  $k_B$  the Boltzmann constant, and T the temperature. The resulting DOS,  $N_c$ , is then calculated from the classical DOS  $N_{c,0}$ , which is normally modeled as a constant throughout the semiconductor, with the correction factor  $h_{corr}$  as

$$N_{\rm c} = N_{\rm c,0} h_{\rm corr} \,.$$

(2.108)

The interplay of the different parameters and the distance to the Si/SiO<sub>2</sub> interface is schematically depicted in Figure 2.5. The parameter  $z_0$  is important, because with  $z_0 = 0$  the DOS at the interface becomes zero. This would cause numerical problems and reduce the convergence of the numerical solver. A positive number of  $z_0$  shifts the correction function towards the dielectric,

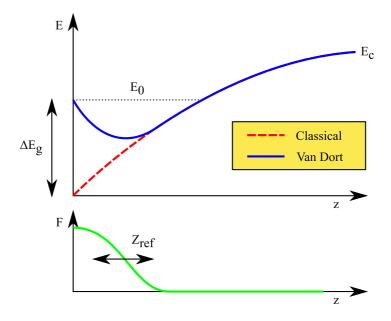

Figure 2.6: Band edge bending at the Si/SiO<sub>2</sub> interface. The classical band edge is corrected by the factor  $\Delta E_{\rm g} F(z)$ .

approximately considering wave function penetration. The value of  $\zeta \lambda_{\rm TH}$  defines the effective depth of the correction. A high value, which can be achieved with  $\zeta > 1$ , leads to a reduction of the DOS even deep in the substrate.

Note that the correction factor does not depend on the bias and the band edge energies are not influenced. Hence, the model can be evaluated in a preprocessing step and does not impose any additional computational burden during iteration steps.

## 2.4.1.2 Conduction Band Edge Correction

An alternative approach is based on  $E_0$ , the first eigenvalue of the triangular energy well, as seen in Figure 2.6. This model was proposed by van Dort [12]

$$\Delta E_{\rm g} = E_0 - E_{\rm c}(0) = \frac{13}{9} \beta \left(\frac{\varepsilon_{\rm si}}{4 {\rm qk_B} T}\right)^{1/3} |E_{\rm n}|^{2/3},$$

(2.109)

where the proportionality factor  $\beta = 4.1 \times 10^{-8} \,\mathrm{eVcm}$  is is found from the observed threshold voltage shift at high doping levels [13],  $\varepsilon_{\rm si}$  is the permittivity of silicon, and  $E_{\rm n}$  is the electric field at the Si/SiO<sub>2</sub> interface perpendicular to the interface.

The value of  $\Delta E_{\rm g}$  is multiplied with a distance-dependent weight function which has been introduced by Selberherr [14] for the modeling of surface roughness scattering in MOSFETs. The function is of the following form

$$F(z) = \frac{2\exp(-(z/z_{\text{ref}})^2)}{1 + \exp(-2(z/z_{\text{ref}})^2)},$$

(2.110)

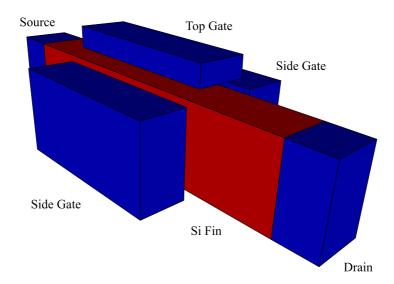

**Figure 2.7:** Device geometry of a triple-gate FinFET structure. Quantum confinement plays an important role in this device because of its small size and the formation of three, instead of one, channels.

where  $z_{\text{ref}}$  is the scaling factor for the interface distance. Thus, the resulting band edge energy with van Dort's quantum correction of the classical band edge energy  $E_{\text{class}}$  reads as follows

$$E_{\rm c} = E_{\rm class} + F(z)\Delta E_{\rm g}. \tag{2.111}$$

Figure 2.6 depicts the distance dependent weight function F and the band edge energy for both, the classical approach and after quantum correction with van Dort's method.

# 2.4.1.3 Evaluation of Quantum Correction Models

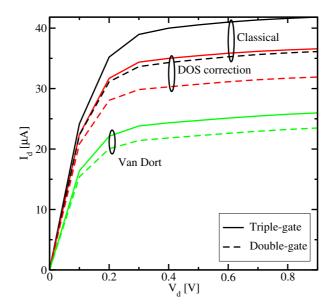

For the evaluation of the quantum correction models a state-of-the-art three-dimensional n-channel FinFET device structure was chosen. The device geometry can be seen in Figure 2.7. The silicon fin has a cross section area of  $6\times10\,\mathrm{nm}^2$ . The gate length is  $20\,\mathrm{nm}$  with a gate oxide thickness of  $1.5\,\mathrm{nm}$ . The source and drain regions are heavily n-type doped whereas the channel itself remains undoped.

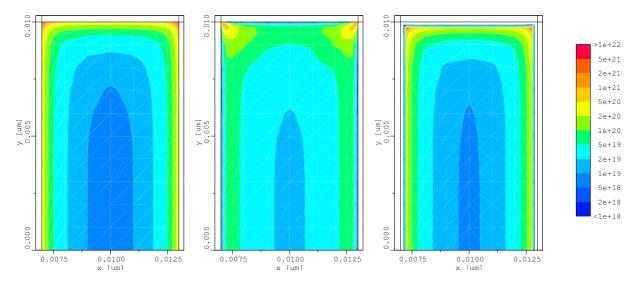

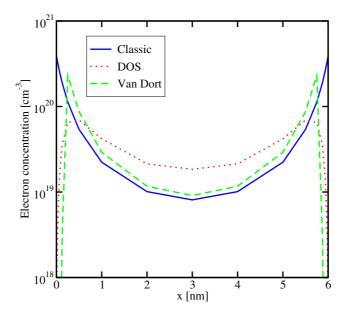

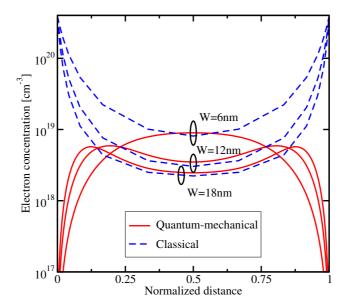

Figure 2.8 depicts the electron concentration in a two-dimensional cut through the silicon fin in the middle of the channels. The gates are biased at 0.9 V with the source and drain contacts grounded. The classical simulation using the drift-diffusion approximation gives the highest magnitude of the electron concentration at the Si/SiO<sub>2</sub> interfaces below the gate contacts. It can be seen that the peak electron concentration is found in the top corners, as two respective gates couple to the channel, each of them attracting carriers. With the quantum confinement correction models the maximum carrier concentration is moved to the inside of the fin by a distance depending on the chosen model and its calibration parameters.

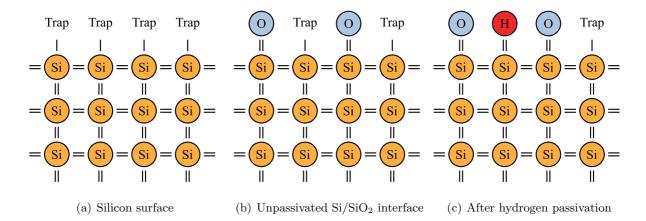

Figure 2.8: Electron concentration in a triple-gate FinFET for classical simulation (left), with the DOS correction model (middle), and the band edge energy correction model by Van Dort. The correction models force the peak of the carrier concentration away from the Si/SiO<sub>2</sub> interface into the substrate.

**Figure 2.9:** Electron concentration across the fin using classical device simulation and the confinement correction models.

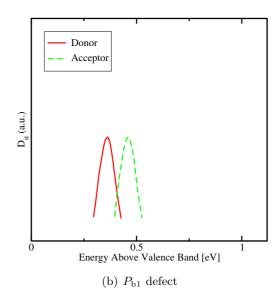

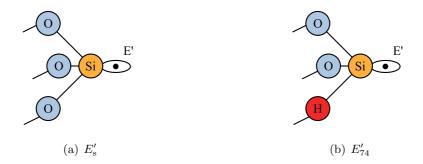

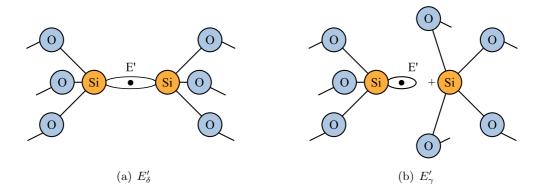

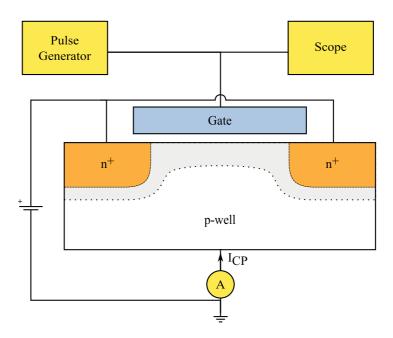

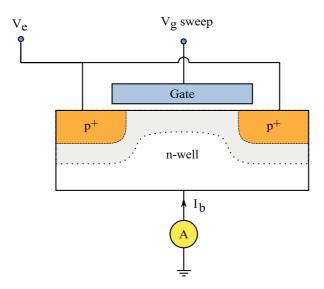

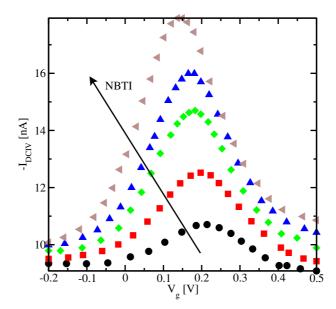

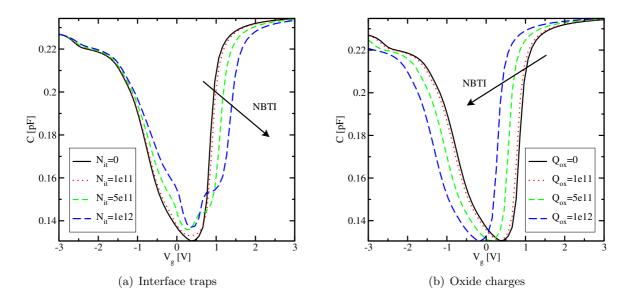

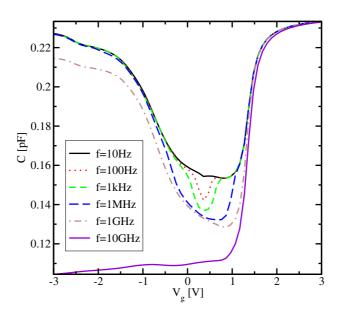

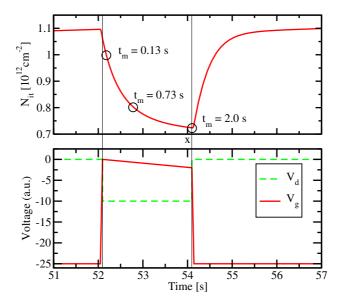

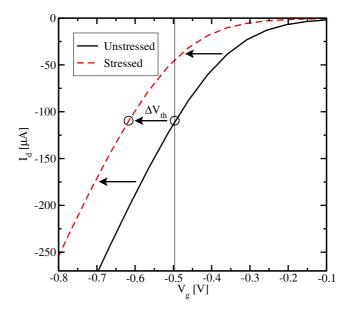

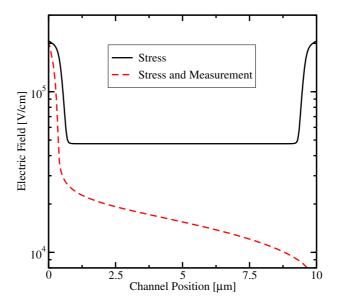

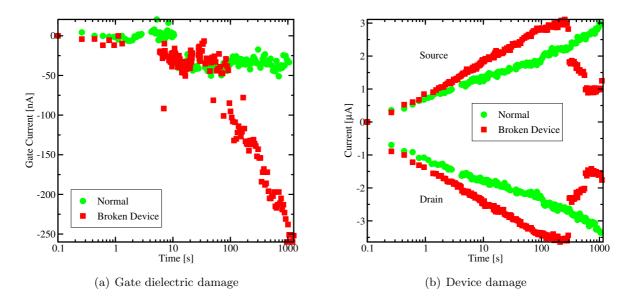

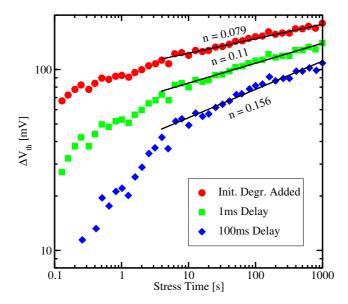

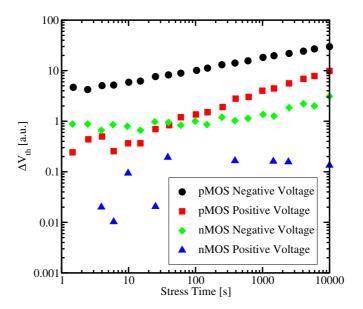

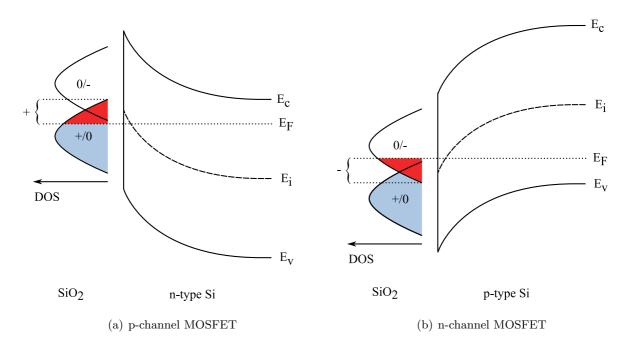

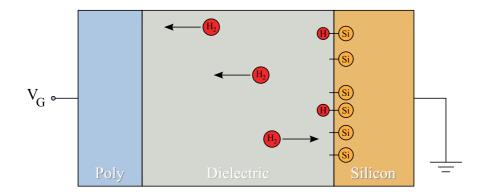

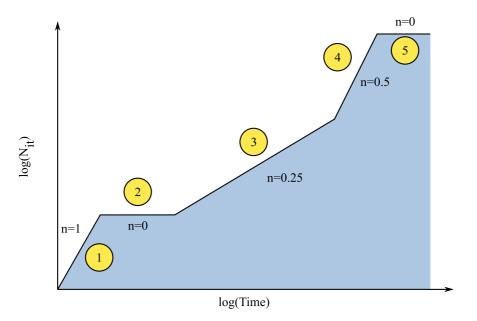

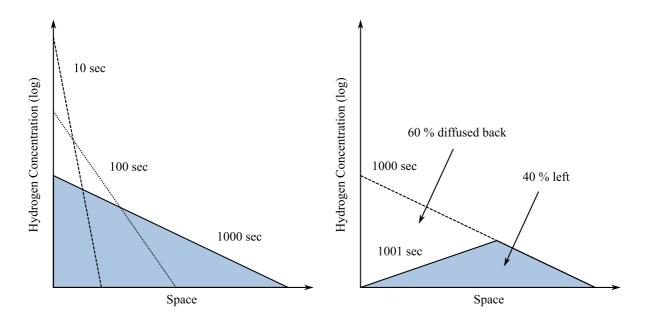

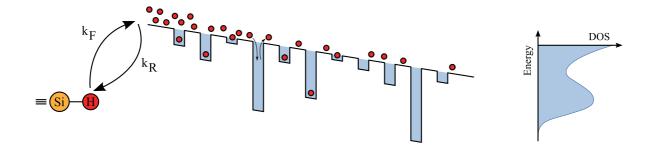

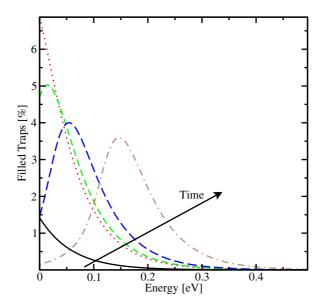

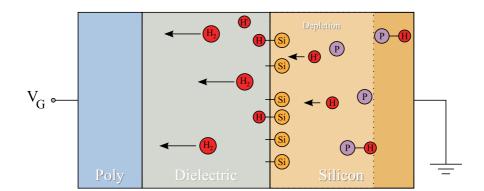

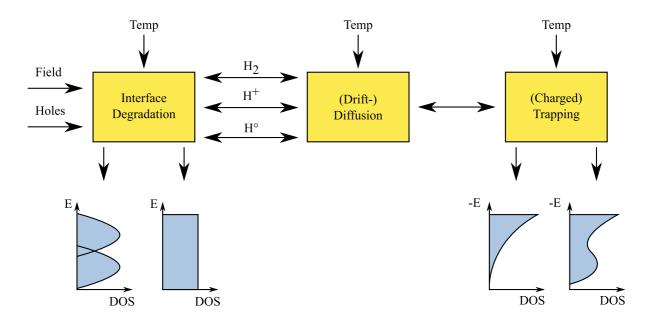

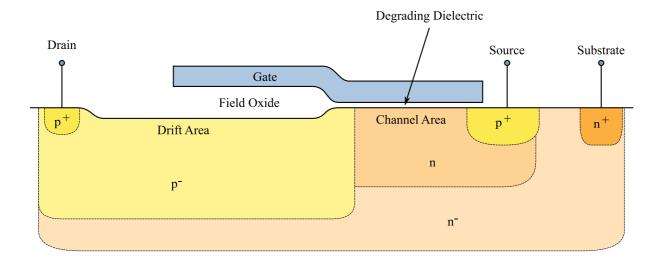

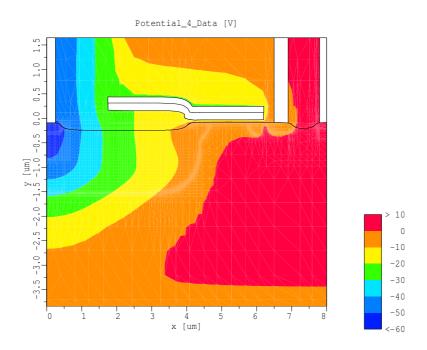

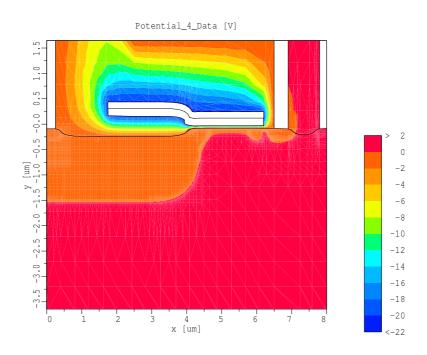

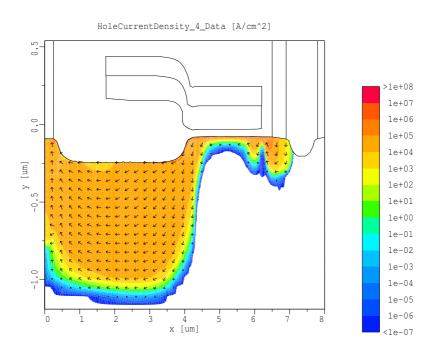

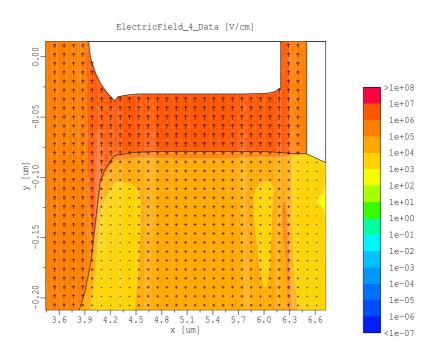

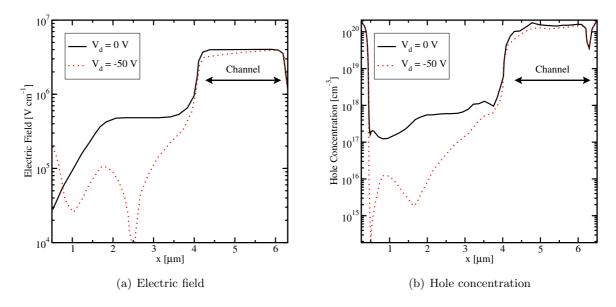

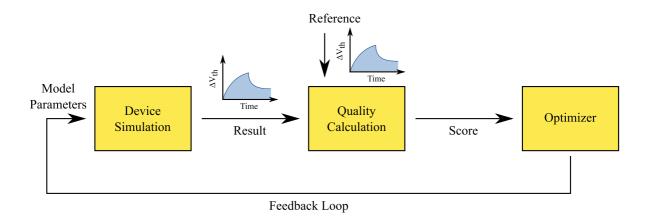

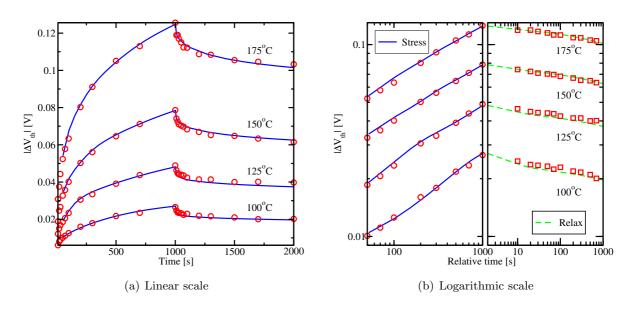

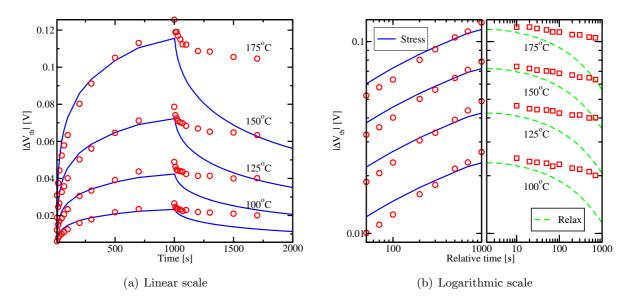

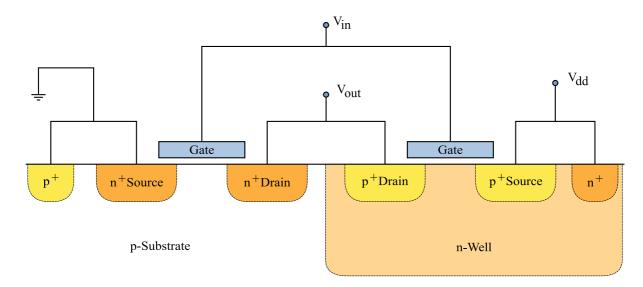

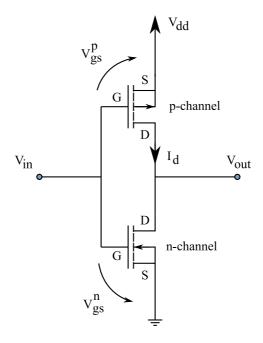

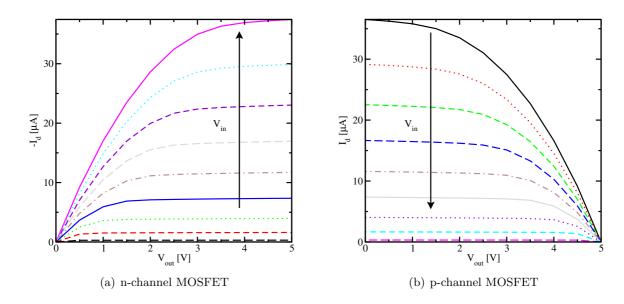

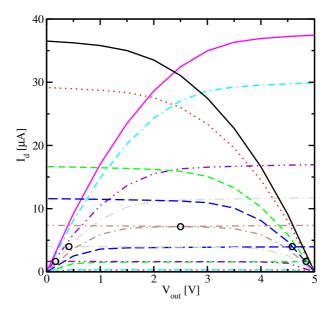

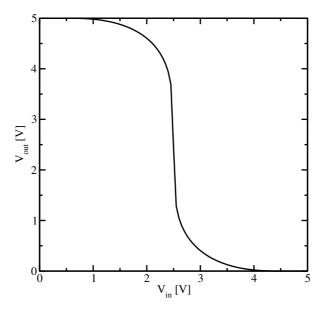

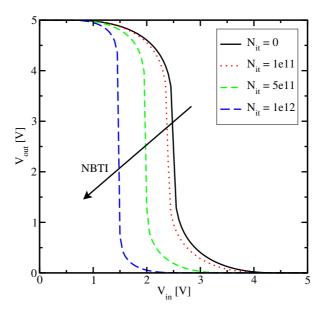

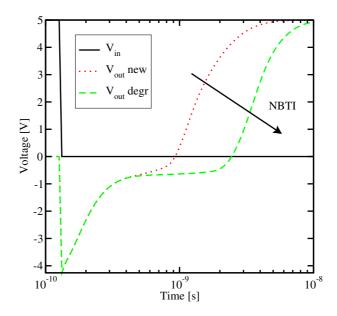

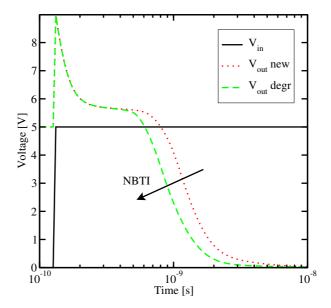

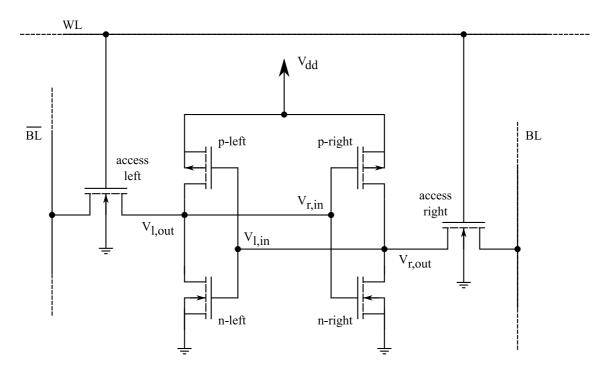

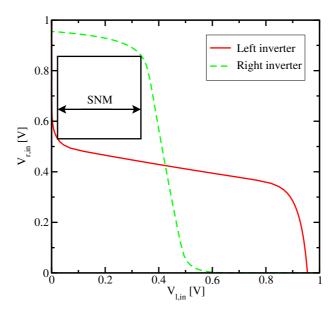

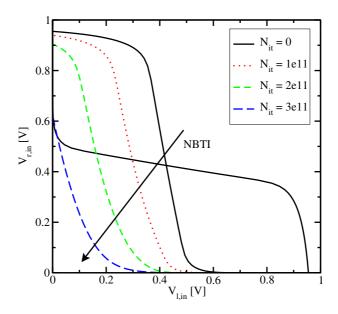

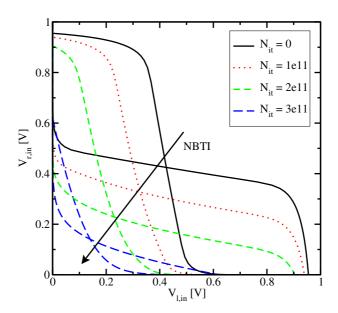

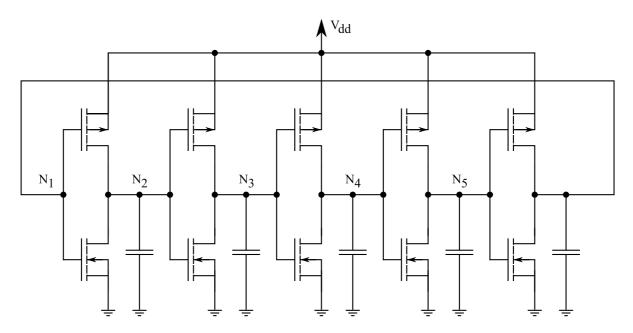

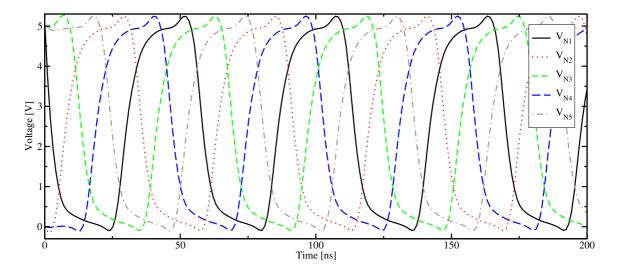

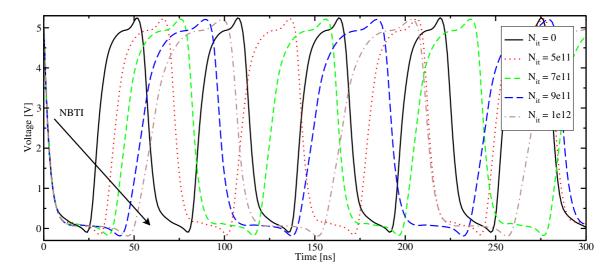

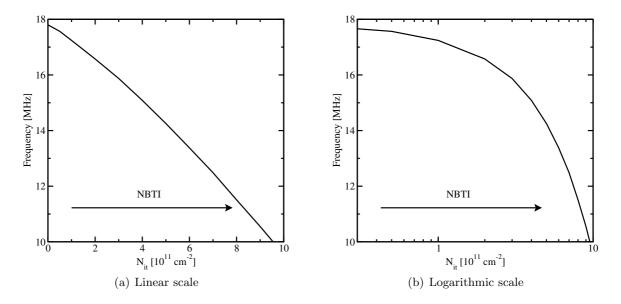

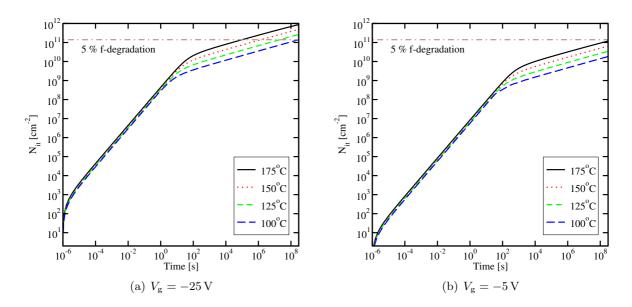

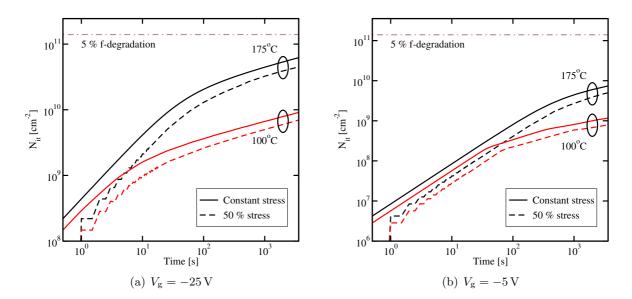

**Figure 2.10:** Comparison of classical and quantum mechanical carrier concentrations for different fin widths. The quantum mechanical calculations have been performed using a Schrödinger solver.